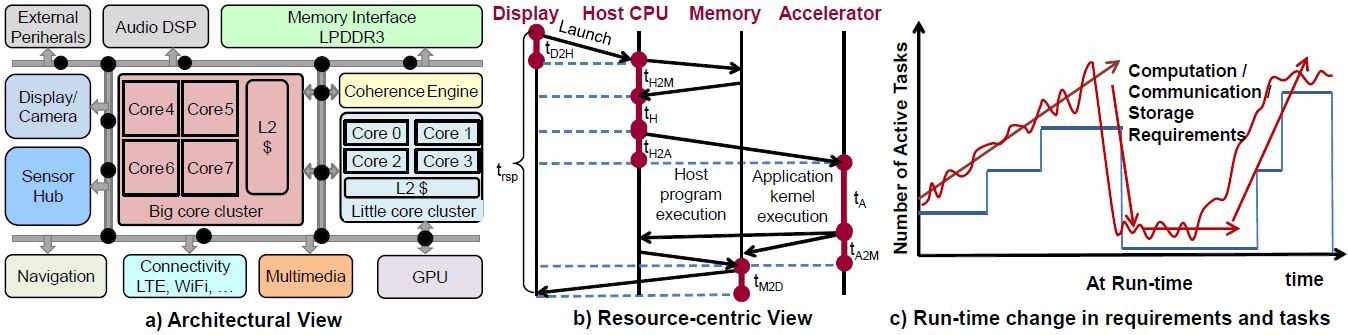

Dynamic reconfiguration techniques including dynamic cache reconfiguration (DCR), dynamic voltagefrequency

scaling (DVFS), and dynamic reconfiguration of computation and communication architectures

are widely used for designing efficient systems. Although these techniques have received considerable attention

from various domains in recent years, dynamic reconfiguration techniques are not employed in real-time

System-on-Chip (SoC) designs. This is due to the fact that real-time systems may consist of critical tasks

with soft or hard deadlines, and the additional computation required for dynamic reconfiguration may adversely

affect the critical tasks. Missing deadlines may lead to performance degradation or even catastrophic

failures in these systems. The goal of this proposal is to develop a comprehensive dynamic reconfiguration

framework to enable adaptive computation, communication and storage in heterogeneous multicore SoCs

under power, performance, energy, temperature, reliability and real-time constraints.

| |

Faculty (PI) |

|

Ph.D. Students |

|

M.S. Students |

|

Undergraduate (REU) Researchers |

| |

Prof. Prabhat Mishra (UF) |

|

Yuanwen Huang (Google) |

|

Anirudh Canumalla |

|

Timon Angerhofer, Lisbeth Cardoso |

| |

|

|

Subodha Charles, Yangdi Lyu |

|

Chetan A. Patil |

|

Kevin Barta, John Zoldos |

| |

|

|

Alif, Ahmed, Hadi Hajimiri |

|

|

|

Meredith Agens, Alexander Rumak |

| |

Prof. Umit Ogras (ASU) |

|

Ujjwal Gupta (Intel) |

|

|

|

Nikhil Venkatesh, Stephen Butler |

| |

|

|

Ganapati Bhat |

|

|

|

Megan Logan, Miranda Overstreet |

| |

|

|

Sumit K. Mandal |

|

|

|

Audrey Mendez, Hongquy Nguyen |

| J7 |

Subodha Charles, Alif Ahmed, Umit Ogras and Prabhat Mishra, Efficient Cache Reconfiguration using Machine Learning in NoC-based Many-Core CMPs, ACM Transactions on Design Automation of Electronic Systems (TODAES), 24(6), Article 60, September 2019. |

| J6 |

Alif Ahmed, Yuanwen Huang and Prabhat Mishra, Cache Reconfiguration using Machine Learning for Vulnerability-aware Energy Optimization, ACM Transactions on Embedded Computing Systems (TECS), 8(2), Article 15, March 2019. |

| J5 |

Yuanwen Huang and Prabhat Mishra, Vulnerability-aware Energy Optimization for Reconfigurable Caches in Multitasking Systems, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 38(5), pages 809-821, May 2019. |

| J4 |

Ujjwal Gupta, Chetan Patil, Ganapati Bhat, Prabhat Mishra and Umit Ogras, DyPO: Dynamic Pareto Optimal Configuration Selection for Heterogeneous MpSoCs, ACM Transactions on Embedded Computing Systems (TECS), 16(5), pages 123:1-123:20, October 2017. |

| J3 |

Ujjwal Gupta, Sumit K. Mandal, Manqing Mao, Chaitali Chakrabarti and Umit Y. Ogras, A Deep Q-Learning Approach for Dynamic Management of Heterogeneous Processors, IEEE Computer Architecture Letters, 18(1), 14-17, 2019. |

| J2 |

Ganapati Bhat, Gaurav Signla, Ali K. Unver and Umit Y. Ogras, Algorithmic Optimization of Thermal and Power Management for Heterogeneous Mobile Platforms, IEEE Transanctions on VLSI Systems, 26(3), 544-557, 2018. |

| J1 |

Ganapati Bhat, Suat Gumussoy and Umit Ogras, Power-temperature stability and safety analysis for multiprocessor systems, ACM Transactions on Embedded Computing Systems (TECS), 16(5), 2017. |

| C10 |

Yuanwen Huang and Prabhat Mishra, Vulnerability-aware Dynamic Reconfiguration of Partially Protected Caches, IEEE International Symposium on Quality Electronic Design (ISQED), Santa Clara, California, March 25 - 26, 2020. |

| C9 |

Subodha Charles, Yangdi Lyu, Prabhat Mishra, Real-time Detection and Localization of DoS Attacks in NoC based SoCs, Design Automation and Test in Europe (DATE), Florence, Italy, March 25 - 29, 2019. |

| C8 |

Ganapati Bhat, Suat Gumussoy, Umit Y. Ogras, Power and Thermal Analysis of Commercial Mobile Platforms: Experiments and Case Studies, Design Automation and Test in Europe (DATE), Florence, Italy, March 25 - 29, 2019. |

| C7 |

Ujjwal Gupta, Manoj Babu, Raid Ayoub, Michael Kishinevsky, Francesco Paterna and Umit Y. Ogras, STAFF: Online Learning with Stabilized Adaptive Forgetting Factor and Feature Selection Algorithm, Design Automation Conference (DAC), 2018. |

| C6 |

Subodha Charles, Hadi Hajimiri and Prabhat Mishra, Proactive Thermal Management using Memory-based Computing in Multicore Architectures, International Green and Sustainable Computing Conference (IGSC), Pittsburgh, October 22-24, 2018. |

| C5 |

Subodha Charles, Chetal Patil, Umit Ogras and Prabhat Mishra, Exploration of Memory and Cluster Modes in Directory-Based Many-Core CMPs, IEEE/ACM International Symposium on Networks-on-Chip (NOCS), Torino, Italy, October 4-5, 2018. |

| C4 |

Yuanwen Huang and Prabhat Mishra, Vulnerability-aware Energy Optimization using Cache Reconfiguration and Partitioning in Multicore Systems, IEEE International Conference on Computer Design (ICCD), pages 241-248, Boston, Massachusetts, November 5 - 8, 2017. |

| C3 |

Yuanwen Huang and Prabhat Mishra, Reliability and Energy-aware Cache Reconfiguration for Embedded Systems, IEEE International Symposium on Quality Electronic Design (ISQED), pages 313-318, Santa Clara, California, March 15-16, 2016. Best Paper Award |

| C2 |

Zhe Wang, Sanjay Ranka and Prabhat Mishra, Efficient Task Partitioning and Scheduling for Thermal Management in Multicore Processors, IEEE International Symposium on Quality Electronic Design (ISQED), pages -, Santa Clara, California, March 2-4, 2015. |

| C1 |

Hadi Hajimiri, Kamran Rahmani and Prabhat Mishra, Efficient Peak Power Estimation using Probabilistic Cost-Benefit Analysis, International Conference on VLSI Design, pages 369-374, Bengaluru, India, January 3-7, 2015. |