SigSeT: Signal Selection Tool for Post Silicon Validation

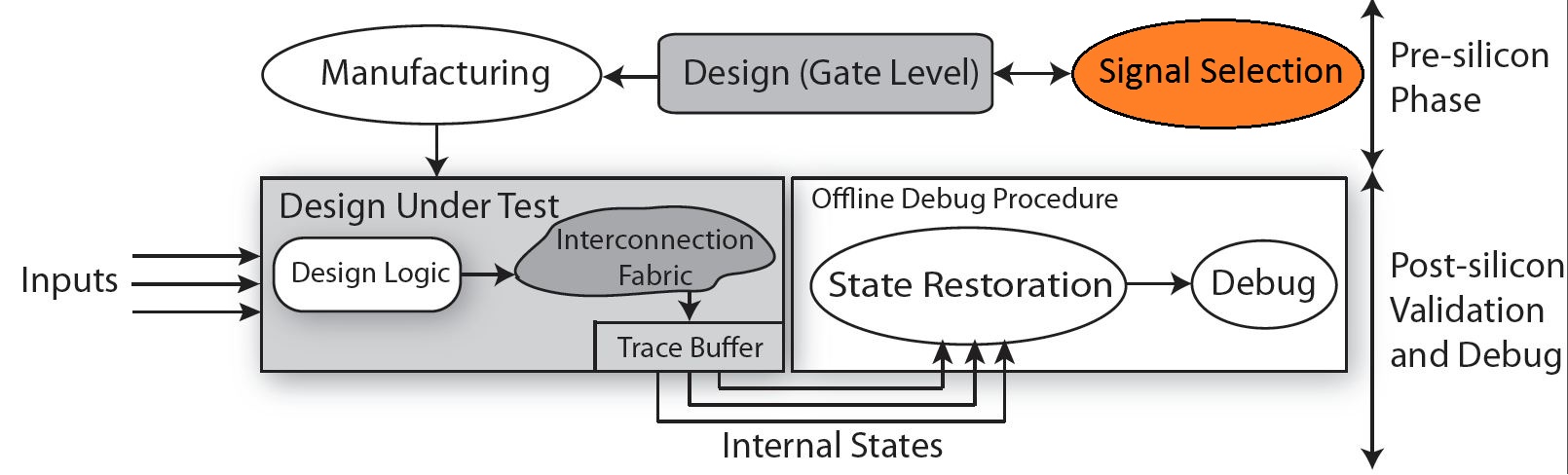

This tool takes as input a logic circuit specified in the ISCAS'89 format and returns the profitable trace signals based on two algorithms outlined in Basu and Mishra [J1] and Rahmani, Mishra and Ray [J2]. The first one is based probability analysis and the second one is based on linear programming formulation. This tool can be used during signal selection phase as outlined in Figure 1. During design phase, the selected signals need to be routed to a trace buffer. During execution, these signals will be traced and stored in the trace buffer. Once a failure is detected, the stored signal states can be used to reconstruct the unknown signal states in order to localize an error.

|

Tool Download

| Version 0.1 | Jun 21, 2013 | Algorithm developed by Basu and Mishra [J1] | |||||

| Version 0.2 | May 21, 2015 | Algorithm developed by Kamran, Mishra and Ray [J2] |

Journal Articles

| J1 | Kanad Basu and Prabhat Mishra, Restoration-Aware Trace Signal Selection for Post Silicon Validation, IEEE Transactions on Very Large Scale Integration (VLSI) Systems (TVLSI), 21(4), pages 605-613, April 2013. |

| J2 | Kamran Rahmani, Prabhat Mishra and Sandip Ray, Efficient Trace Signal Selection using Augmentation and ILP Techniques, IEEE International Symposium on Quality Electronic Design (ISQED), pages 148-155, 2014. |

.::

::.