SYSTEM-LEVEL VALIDATION OF MULTICORE ARCHITECTURES

By XIAOKE QIN

# A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# UNIVERSITY OF FLORIDA

© 2012 Xiaoke Qin

I dedicate this to my family.

#### ACKNOWLEDGMENTS

First of all, I truly appreciate the effort of my Ph.D. adviser Prof. Prabhat Mishra. He not only guided me to overcome challenging problems, but also taught me how to explore new directions. More importantly, he is always considerate to me and has helped me building my career. He is the person who made this dissertation come true.

I would like to thank my other Ph.D. committee members: Prof. Sartaj Sahni, Prof. Jih-Kwon Peir, Prof. Greg Stitt and Prof. Ann Gordon-Ross for their valuable comments and suggestions. I also thank my lab-mates, Mingsong Chen, Kanad Basu, Weixun Wang, Chetan Murthy, Kartik Shrivastava, Hadi Hajimiri and Kamran Rahmani. It was my great pleasure to work with them. I really enjoyed our friendship and I hope it will last forever.

Last but not least, I sincerely thank my family for their love and support. They encouraged me to pursue my dreams and become a good person. I would like to give the most special thanks to my girlfriend, Jie. Her love and devotion paved the road to my doctoral degree.

This work was partially supported by grants from National Science Foundation (NSF) CAREER Award 0746261.

# TABLE OF CONTENTS

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                            | paę                                   | ge                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------|

| ACK  | NOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | 4                                                        |

| LIST | T OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 8                                                        |

| LIST | T OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | 9                                                        |

| ABS  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 11                                                       |

| СНА  | APTER                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                                                          |

| 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | 12                                                       |

|      | <ul> <li>1.1 Functional Validation of Multicore Architectures</li></ul>                                                                                                                                                                                                                                                                                                                                                                    | · · ·                                 | 13<br>15<br>16<br>19                                     |

| 2    | RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | 20                                                       |

|      | <ul> <li>2.1 Test Generation for Architecture Validation</li></ul>                                                                                                                                                                                                                                                                                                                                                                         | 2                                     | 20<br>24<br>25                                           |

| 3    | SYNCHRONIZED GENERATION OF DIRECTED TESTS                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                     | 28                                                       |

|      | <ul> <li>3.1 Background .</li> <li>3.1.1 Conflict clause forwarding .</li> <li>3.1.2 Property clustering .</li> <li>3.2 Synchronized Test Generation .</li> <li>3.2.1 Correctness of the Proposed Approach .</li> <li>3.2.2 Implementation Details .</li> <li>3.3 Experiments .</li> <li>3.3.1 A Stock Exchange System .</li> <li>3.3.2 A VLIW MIPS Processor .</li> <li>3.3.3 Circuit Test Generation .</li> <li>3.4 Summary .</li> </ul> |                                       | 29<br>29<br>31<br>37<br>38<br>39<br>39<br>42<br>45<br>46 |

| 4    | EFFICIENT TEST GENERATION FOR MULTICORE ARCHITECTURES .                                                                                                                                                                                                                                                                                                                                                                                    | 4                                     | 48                                                       |

|      | <ul> <li>4.1 Test Generation for Multicore Architectures</li> <li>4.1.1 Correctness of Our Proposed Approach</li> <li>4.1.2 Implementation Details</li> <li>4.1.3 Heterogeneous Multicore Architectures</li> <li>4.2 Experiments</li> <li>4.2.1 Experimental Setup</li> <li>4.2.2 Results</li> </ul>                                                                                                                                       | · · · · · · · · · · · · · · · · · · · | 49<br>55<br>56<br>58<br>60<br>60                         |

|   | 4.3                      | Summary 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | VAL                      | IDATION OF CACHE COHERENCE PROTOCOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.1<br>5.2<br>5.3<br>5.4 | Background and Motivation67Test generation for Transition Coverage695.2.1 SI Protocol705.2.2 MSI Protocol735.2.3 MESI Protocol765.2.4 MOSI Protocol76Experiments78Summary81                                                                                                                                                                                                                                                                                                                                                |

| 6 | SCA                      | LABLE DIRECTED TEST GENERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 6.1<br>6.2<br>6.3<br>6.4 | Directed Test Generation by Interleaving Concrete and Symbolic Execution 846.1.1 Illustrative Example846.1.2 System Model876.1.3 Instrumentation886.1.4 Concrete Simulation906.1.5 Path Constraint Generation916.1.6 Test Generation926.1.7 Constraint Solving Optimization93Implementation Details946.2.1 Design Flattening946.2.2 Clock Cycle Population956.2.3 Dynamic Array Reference Disambiguation95Experiments966.3.1 Designs without Dynamic Array References976.3.3 SAT-based BMC versus Our Approach99Summary101 |

| 7 |                          | IPERATURE- AND ENERGY-CONSTRAINED SCHEDULING IN REAL-TIME         STEMS       102                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 7.1<br>7.2<br>7.3        | Background and Problem Formulation1027.1.1 Thermal Model1027.1.2 Energy Model1037.1.3 System Model1037.1.4 TCEC problem104Overview106Approximation Algorithm for TCEC Scheduling1077.3.1 Notations1077.3.2 TCEC as MCP1087.3.3 An Exact Algorithm for MCP1117.3.4 Approximation Algorithm114                                                                                                                                                                                                                               |

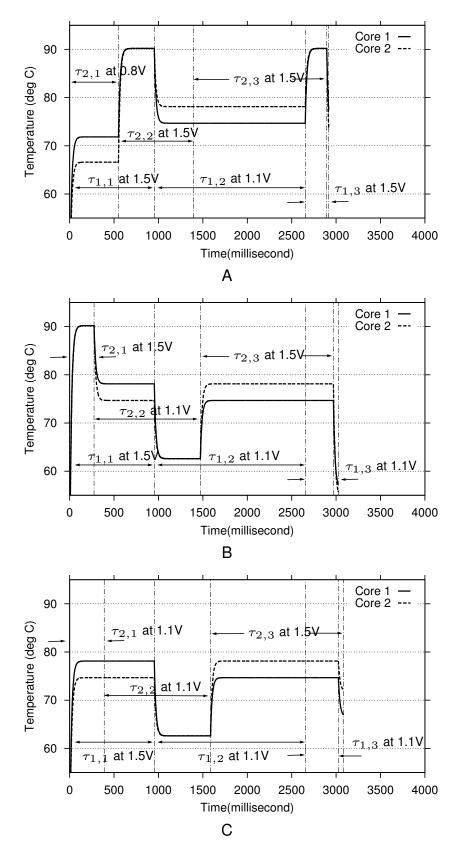

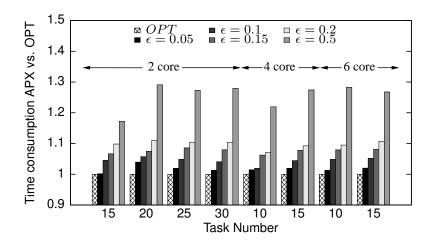

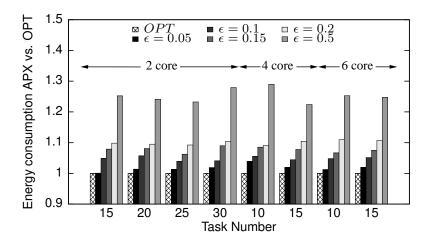

|      | <ul><li>7.4</li><li>7.5</li><li>7.6</li></ul> | Problem Variants122Experiments1247.5.1Experimental Setup1247.5.2TCEC versus TC or EC1247.5.3TCEC using Approximation Algorithm126Summary129                                                                                                                                                                                           |

|------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | SCH                                           | EDULABILITY VALIDATION FOR MULTICORE ARCHITECTURES 130                                                                                                                                                                                                                                                                                |

|      | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6        | Background and Problem Formulation1308.1.1Processor Thermal Model1308.1.2Energy Model1318.1.3System Model1318.1.4Multicore DVS Schedule1318.1.5Problem Formulation132Optimal Algorithm for TECS132Approximation Algorithm138Problem Variants1488.4.1Task Set with Dependence1488.4.2Hard Energy Constraint149Experiments149Summary153 |

| 9    | CON                                           | ICLUSIONS AND FUTURE WORK                                                                                                                                                                                                                                                                                                             |

|      | 9.1<br>9.2                                    | Conclusions       154         Future Research Directions       156                                                                                                                                                                                                                                                                    |

| REF  | ERE                                           | NCES                                                                                                                                                                                                                                                                                                                                  |

| BIOC | GRAF                                          | PHICAL SKETCH                                                                                                                                                                                                                                                                                                                         |

# LIST OF TABLES

| Table |                                                                     |   | age |

|-------|---------------------------------------------------------------------|---|-----|

| 3-1   | Test generation time comparison for OSES                            |   | 40  |

| 3-2   | Test generation time comparison for MIPS                            |   | 44  |

| 3-3   | Test generation time comparison for circuits                        |   | 46  |

| 4-1   | Test generation time for 8 core system                              |   | 62  |

| 4-2   | Detailed test generation information                                |   | 62  |

| 5-1   | Statistics of our test generation algorithm for different protocols |   | 79  |

| 6-1   | Verilog instrumentation code                                        |   | 89  |

| 6-2   | Comparison with HYBRO [56]                                          |   | 97  |

| 6-3   | Comparison with random testing                                      |   | 98  |

| 6-4   | Comparison with BMC [22]                                            | • | 100 |

| 7-1   | Running time comparison on different task sets                      | • | 127 |

| LIST | OF | FIGL | JRES |

|------|----|------|------|

|------|----|------|------|

| Figu | lre                                                                                                                                                                                                           | ра | age |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

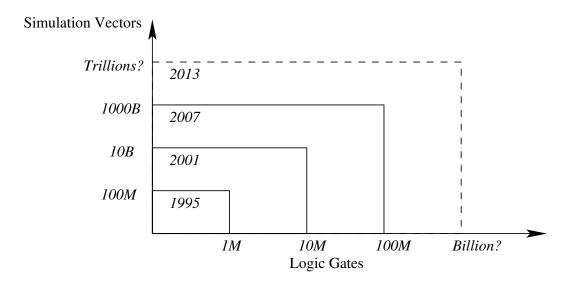

| 1-1  | Simulation effort growth with design complexity                                                                                                                                                               |    | 14  |

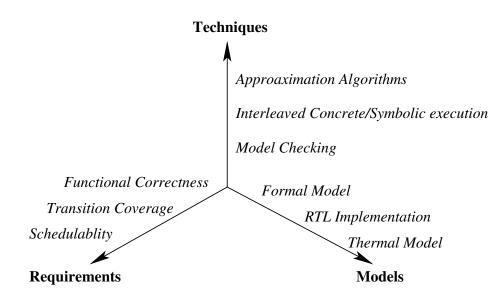

| 1-2  | Design validation models, requirements and techniques                                                                                                                                                         |    | 17  |

| 1-3  | Dissertation outline                                                                                                                                                                                          |    | 17  |

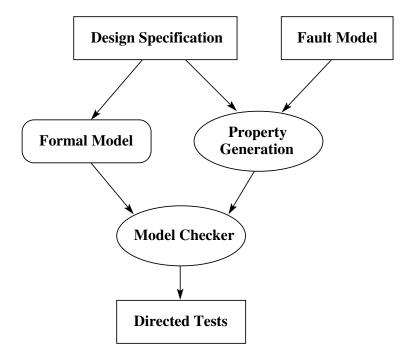

| 2-1  | Directed test generation flow                                                                                                                                                                                 |    | 20  |

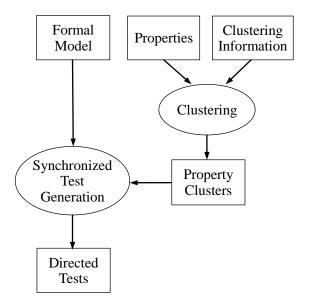

| 3-1  | Synchronized Test Generation                                                                                                                                                                                  |    | 31  |

| 3-2  | Different incremental SAT solving techniques                                                                                                                                                                  |    | 32  |

| 3-3  | Synchronized test generation for multiple properties                                                                                                                                                          |    | 36  |

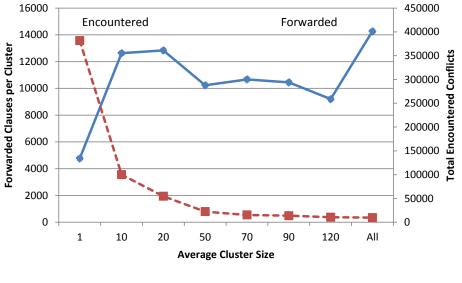

| 3-4  | Test generation for OSES using different cluster size                                                                                                                                                         |    | 43  |

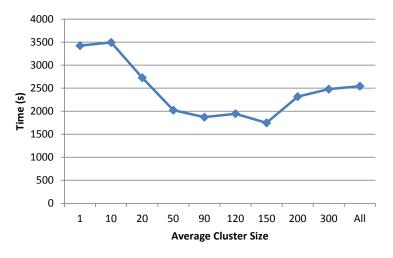

| 3-5  | Test generation for MIPS using different cluster size                                                                                                                                                         |    | 45  |

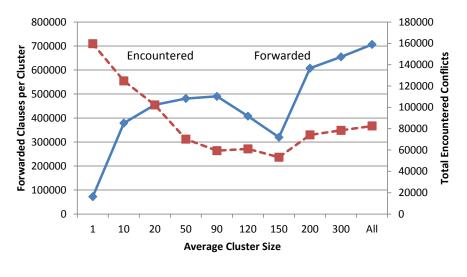

| 3-6  | Test generation for circuits using different cluster size                                                                                                                                                     |    | 47  |

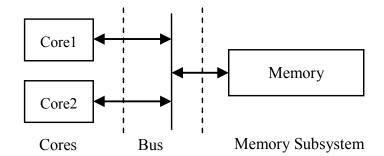

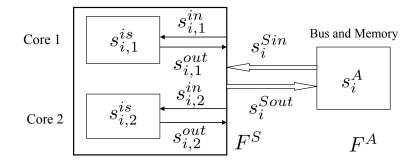

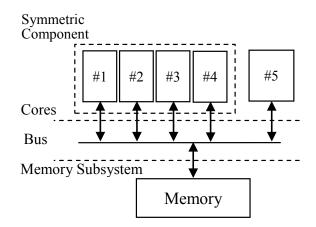

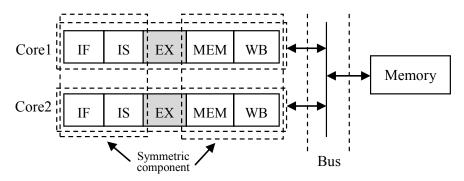

| 4-1  | Abstracted architecture of a two core system                                                                                                                                                                  |    | 49  |

| 4-2  | Incremental SAT solving technique [79]                                                                                                                                                                        |    | 50  |

| 4-3  | Test generation for multicore architectures                                                                                                                                                                   |    | 50  |

| 4-4  | FSM representation of Figure 4-1 at time step <i>i</i>                                                                                                                                                        |    | 51  |

| 4-5  | Test generation for multicore architectures                                                                                                                                                                   |    | 54  |

| 4-6  | Multicore system with different types of cores                                                                                                                                                                |    | 59  |

| 4-7  | Multicore system with different types of execution units                                                                                                                                                      |    | 59  |

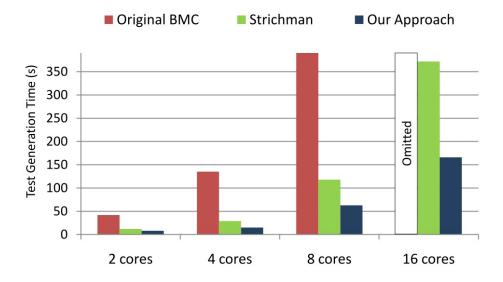

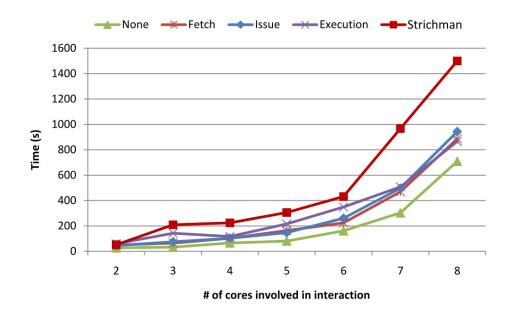

| 4-8  | Test generation time with different number of cores                                                                                                                                                           |    | 61  |

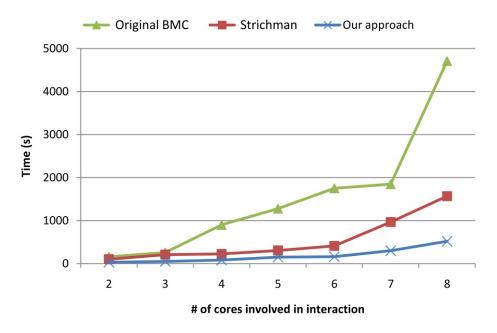

| 4-9  | Test generation time with different interactions                                                                                                                                                              |    | 63  |

| 4-10 | Test generation time with heterogeneous cores                                                                                                                                                                 |    | 64  |

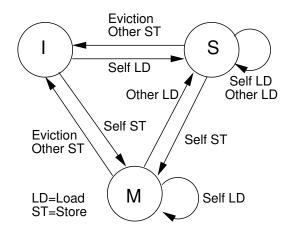

| 5-1  | State transitions for a cache block in MSI protocol                                                                                                                                                           |    | 68  |

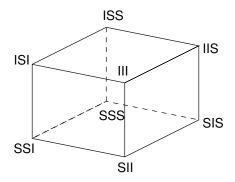

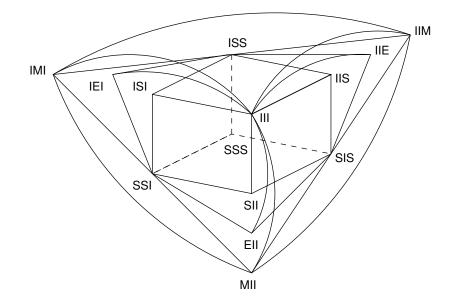

| 5-2  | Global FSM state space of SI protocol with 3 cores                                                                                                                                                            |    | 71  |

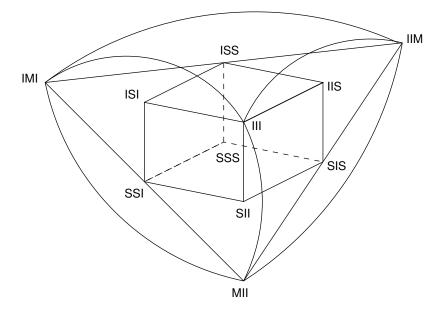

| 5-3  | State space of MSI protocol with 3 cores. For the clarity of presentation, the transitions to global modified states (IIM, IMI, MII) are omitted, if the transition in the opposite direction does not exist. |    | 74  |

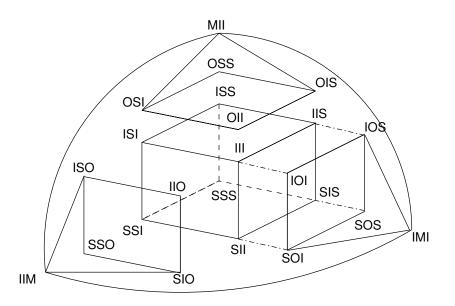

| 5-4  | State space of MESI protocol with 3 cores                                                                                                                                                                     |    | 77  |

|      |                                                                                                                                                                                                               |    |     |

| 5-5 | State space of MOSI protocol with 3 cores                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

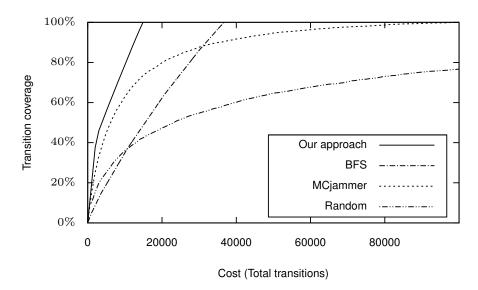

| 5-6 | Transition coverage vs. cost for different test generation methods on MESI protocol with 8 cores                                          |

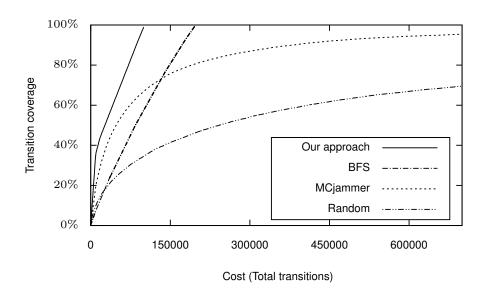

| 5-7 | Transition coverage vs. cost for different test generation methods on MOSIprotocol with 8 cores80                                         |

| 6-1 | The workflow of our approach                                                                                                              |

| 6-2 | Counter.v                                                                                                                                 |

| 6-3 | Sample Trace                                                                                                                              |

| 6-4 | Sample Path Constraints                                                                                                                   |

| 6-5 | Chronological Back Tracking                                                                                                               |

| 6-6 | Path constraint file structure                                                                                                            |

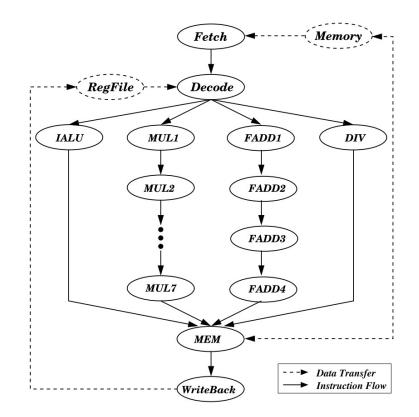

| 6-7 | The MIPS architecture [22]                                                                                                                |

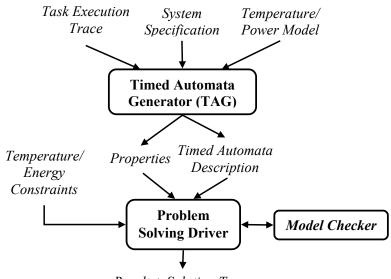

| 7-1 | Overview of our TCEC schedulability framework                                                                                             |

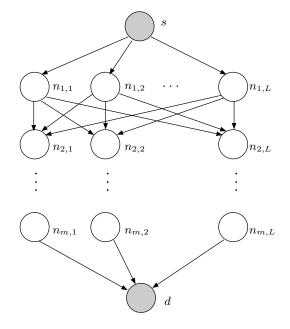

| 7-2 | Job execution graph                                                                                                                       |

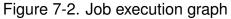

| 7-3 | JEG of TCEC. The values next to each edge are corresponding time and energy consumption                                                   |

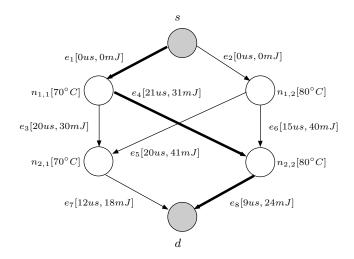

| 7-4 | Possible false negative region. $\epsilon = 0.1$                                                                                          |

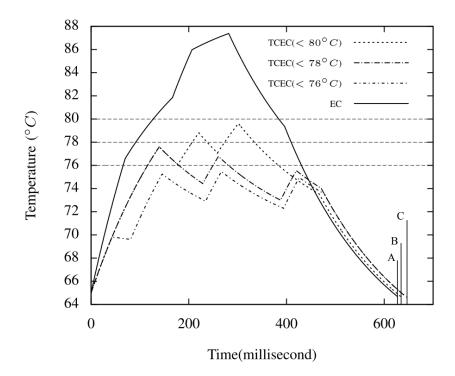

| 7-5 | EC vs TCEC. EC finishes at A. TCEC( $< 80^{\circ}C$ ) finishes at B. Both TCEC( $< 78^{\circ}C$ ) and TCEC( $< 76^{\circ}C$ ) finish at C |

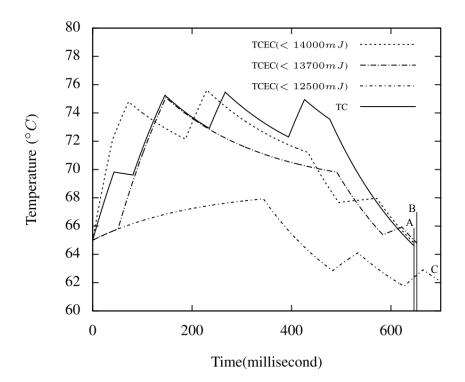

| 7-6 | EC vs TCEC. Both TC and TCEC( $< 14000mJ$ ) finish at A. TCEC( $< 13700mJ$ ) finishes at B. TCEC( $< 12500mJ$ ) finishes at C             |

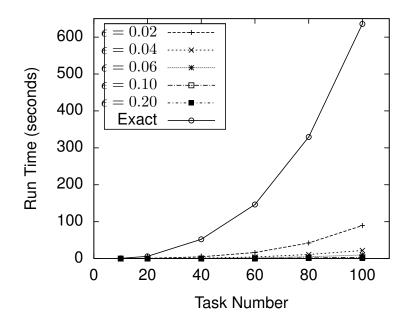

| 7-7 | Running time with different job set size and $\epsilon$                                                                                   |

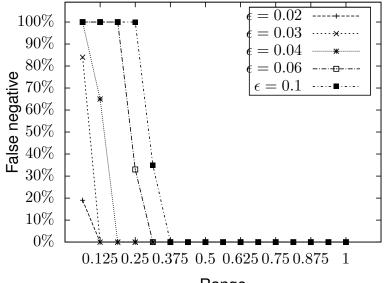

| 7-8 | Accuracy of $EBF_{\epsilon}$                                                                                                              |

| 8-1 | State exploration in Algorithm 9                                                                                                          |

| 8-2 | Precedence relations among tasks                                                                                                          |

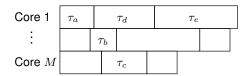

| 8-3 | Temperature and energy constrained scheduling                                                                                             |

| 8-4 | Actual time consumption of $DPRA_{\epsilon}$                                                                                              |

| 8-5 | Actual energy consumption of $DPRA_{\epsilon}$                                                                                            |

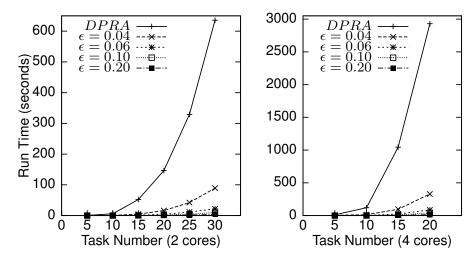

| 8-6 | Running time with different job set size and $\epsilon$                                                                                   |

Abstract of dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

## SYSTEM-LEVEL VALIDATION OF MULTICORE ARCHITECTURES

By

Xiaoke Qin

May 2012

## Chair: Prabhat Mishra Major: Computer Engineering

Multicore processors are widely used in today's servers, desktop and embedded systems. It is a major challenge to verify functional correctness as well as non-functional requirements of multicore architectures. Direct application of existing functional validation approaches usually consumes too much time to reach the coverage goal due to the complexity of multicore designs. Escaped bugs can lead to serious consequences in many scenarios. Due to parallel execution of task sets, existing approaches are also insufficient to validate whether applications in such systems can be scheduled within the given temperature, energy, and timing constraints. If these constraints are violated, it can lead to performance degradation or even catastrophic consequences in safety-critical systems. This dissertation presents novel techniques to address validation challenges of both functional and non-functional requirements in modern multicore architectures. My research has made four major contributions: i) it proposes efficient directed test generation techniques that exploit symmetry in multicore designs; ii) it proposes a novel test generation approach for state- and transition- coverage in a wide variety of cache coherence protocols; iii) it proposes a scalable directed test generation technique based on interleaved concrete and symbolic execution; and iv) it proposes schedulability validation approaches for task sets in multicore architectures under temperature and energy constraints. Extensive experimental results demonstrate significant improvement in overall validation effort.

## CHAPTER 1 INTRODUCTION

Multicore architectures are widely used in todays desktop, server, and embedded systems. Due to the existence of power wall, conventional single core architectures can no longer deliver the required performance improvement by increasing frequency. Instead, architects integrate more and more cores into the same chip to boost the throughput. By operating multiple cores at a lower frequency, multicore architectures can achieve the same performance with significantly less power consumption compared with a high clock rate monolithic core. For desktop-based systems and servers, the multicore architectures deliver the required throughput keeping pace with today's applications with increasing computation complexity. Due to successful deployment of dual-core and quad-core processors, the next generation processors will have 32, 64 or even hundreds of cores. For embedded systems, the energy efficiency of multicore architectures allows devices to operate for longer time with the same battery capacity. Besides, since multiple cores are sharing the same die, the Printed Circuit Board (PCB) size is also reduced. With the growing demand for green data-centers, long-life computers and handhold devices, multicore architectures will continue to dominate the design of next generation System-on-Chip (SoC) architectures.

Successful multicore designs must satisfy both functional and non-functional requirements. Functional requirements ensure that the processor performs all logical functions as specified by the design specification. Non-functional requirements are imposed to make the design satisfy various design constraints such as area, power, energy, temperature, and performance. Clearly, functional requirements are important, because a buggy (erroneous) design leads to unreliable systems. Depending on application domains, unreliable systems can cause loss of vital information or even disaster. Non-functional requirements are also equally important, because violation of non-functional requirements can also lead to serious consequences. For example,

due to uneven activities on different cores, the die temperature of busy cores can easily reach  $120^{\circ}C$  [16]. If the high die temperature is not well controlled, the transient error occurs more frequently and the device is less reliable. Also, devices that always operate in high temperature usually have much shorter lifespan as shown in industrial studies [82]. To avoid these unwanted scenarios, both functional and non-functional validation must be performed to ensure the success of modern multicore designs.

The rest of this chapter is organized as follows. Section 1.1 and Section 1.2 describe existing validation techniques and associated challenges for validation of functional and non-functional requirements, respectively. Section 1.3 summarizes the contribution of this dissertation. Finally, Section 1.4 outlines the organization of this dissertation.

### 1.1 Functional Validation of Multicore Architectures

While multicore architectures are very successful to boost the throughput, their increasing complexity also introduces significant validation challenges. Most widely used functional validation techniques are based on simulation using random and constrained-random tests [93] [1] [83]. The multicore design is placed within a simulation environment and a test generator feeds random tests into the design. The behavior of the design under test is compared with the golden reference model to detect any functional errors.

As illustrated in Figure 1-1 [77], the verification complexity has grown tremendously in last two decades. For example, in 2007 a typical SoC design (with 100 million gates) used one trillion test vectors for simulation. Due to the increasing complexity of multicore architectures, even trillions of simulation vectors may not be inadequate to achieve the required coverage goal within ever decreasing time-to-market window. Since simulation vectors are generated randomly, it is quite difficult for random tests to activate coverage holes. Directed tests [22] are promising to address this problem. By analyzing the logical structure of the design, a small number of directed tests can activate the

Figure 1-1. Simulation effort growth with design complexity

desired behavior of the system. They can be applied in addition to the random tests to reach the coverage goal with much less time. Unfortunately, most directed tests are manually written, which is time consuming and error-prone. Fully automatic directed test generation schemes are desired to accelerate the verification process of multicore architectures. There are two major objectives in directed test generation. First, the overall validation effort should be minimized by reducing the total number of tests required to achieve the coverage goal. Secondly, test generation time should also be small.

Model checking [13, 28] is promising for automated generation of directed tests. To activate a particular scenario, we can feed the negated version of a property to the model checker, and use the resultant counterexample as a directed test. Due to the state space explosion problem, such a process is usually very time consuming. Since different cores in a multicore design usually contain similar structure, their formal descriptions (such as CNF in SAT-based model checking) also exhibit significant symmetry. We believe such symmetry can be exploited to accelerate the model checking process, because the information we learn from one core may be applied directly to other cores. Unfortunately, this intuitive reasoning is hard to implement because it is very difficult to reconstruct the symmetry from the CNF formula. The high level information is lost during CNF synthesis, and it is inefficient as well as computationally expensive to recover through "reverse engineering" methods.

An important requirement of functional validation is to achieve certain state or transition coverage of the state space of the design. Simulation using random tests is widely used in industry to fulfill this goal. However, due to the symmetric nature of multicore architectures, its state space contains some unique features, which can be utilized to reduce the test length or testing time required to reach the required coverage goal. Although the FSM of each cache controller is easy to understand, the structure of the product FSM for modern cache coherence protocols usually have obscure structures that are hard to analyze. Besides, modern processors usually contain multiple cache levels, which greatly complicates the global state space. Even if the global state space can be described, it is still difficult to find an efficient way to perform traversal in it. In other words, the test generation algorithm must activate all states and transitions with limited number of unnecessary transitions. Moreover, since the state space is very large, the tests usually introduce a large storage overhead. Therefore, it is desirable that the test can be generated on the fly.

#### **1.2 Validation of Non-functional Requirements**

So far we have described the importance of ensuring functional correctness and challenges associated with verifying multicore architectures. It is also equally important to ensure that all the non-functional requirements are met. One of the key challenges is to find whether a given task set can be scheduled on the processor(s) without violating the required temperature and energy constraints. This kind of validation is important to ensure the reliability of multicore designs, because high die temperature leads to more frequent transient errors as well as shorter processor lifespan [82]. Besides, the management of overall energy consumption is also crucial to the success of embedded systems. Since many handheld devices are equipped with multicore processors but still

battery-powered, we need to validate that all important tasks are finished with limited energy consumption.

It is usually very costly to perform such validation, because the manufacturer need to build the full system and test the design by executing real task sets. Detection of failures at this stage is expensive, since it will lead to re-design of the system. Since the worst case behavior of real-time systems usually can be obtained by offline analysis, we believe it is possible to predict the system behavior based on the information collected via static analysis of task sets and execution environment. In other words, in various cases, non-functional validation can be performed without running the actual system in real environments. The major challenge in this field comes from the NP-hard nature [103] [100] [86] of the schedulability problem. In fact, it is NP-hard even to verify the schedulability of a task set under temperature and energy constraints in a single core processor. The problem is more complex when the system contains multiple cores.

#### **1.3 Research Contributions**

My research proposes novel techniques to address challenges in both functional and non-function validation of multicore systems. The objective of my research is to develop efficient test generation approaches and validation algorithms for modern multicore architectures.

Figure 1-2 presents the scope of this dissertation. The proposed research develops efficient validation techniques to address different functional and non-functional requirements using a wide variety of design models including system-level models, formal models as well as RTL models.

Figure 1-3 outlines the four major research contributions of this dissertation that are summarized as follows. The first three are related to verifying functional correctness whereas the last one ensure that the non-functional requirements are satisfied.

*Directed test generation for multicore architectures:* This work proposes a novel technique that exploits temporal, structural, and spatial symmetry in multicore designs

Figure 1-2. Design validation models, requirements and techniques

| Multicore System Validation Challenges                                                                                  |                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| Functional Requirements                                                                                                 | Non-functional Requirements                                              |  |

| BMC–based Directed Test Generation ( <i>Chapter 3 and 4</i> )<br>Cache ProtocolTransition Coverage ( <i>Chapter 5</i> ) | Schedulablity Validaition<br>Under Energy and<br>Temperature Constraints |  |

| Scalable Test Generation (Chapter 6)                                                                                    | (Chapter 7 and 8)                                                        |  |

Figure 1-3. Dissertation outline

at the same time. Our proposed technique enables the reuse of the knowledge learned from one core to the remaining cores in multicore architectures (structural symmetry), from one bound to the next for a given property (temporal symmetry), as well as from one property to other properties (spatial symmetry). Our experimental results on both hardware and software designs demonstrate an order-of-magnitude reduction in overall test generation time.

*Efficient test generation for state and transition coverage in cache coherence protocols:* This work proposes an efficient test generation approach for a wide variety of cache coherence protocols. Based on detailed analysis of the space structure, our approach creates efficient test sequences for different parts of the global FSM state space to achieve 100% state and transition coverage for each cache coherence protocol. We develop a graphical description of the state space structure of several commonly used cache coherence protocols and present an on-the-fly directed test generation algorithm based on the Euler tour of hypercubes. The experimental results on different cache coherence protocols show the effectiveness of our approach on systems with many cores.

Scalable directed test generation for real HDL designs: This work develops a scalable technique to enable directed test generation of HDL models by incorporating static analysis and simulation based validation. By performing interleaved concrete and symbolic execution, our approach avoids the error-prone design translation process and enables directed test generation for real designs. Compared with existing approaches based on combined concrete and symbolic execution, our approach avoids the errory references. The experimental results illustrate that our proposed technique is scalable, and enables directed test generation for real designs.

Temperature- and energy-constrained scheduling for multicore architectures: This work explores the DVS scheduling problem on multicore systems under both temperature and energy constraints. We show that this problem is NP-hard even when the steady state temperature is considered. We also present an exact algorithm and a polynomial time approximation scheme for the problem. When the original problem is schedulable, our approximation algorithm is guaranteed to generate a solution, which will not violate the temperature constraint, and consume no more time or energy than a specified approximation bound, e.g., within 1% of the optimal time consumption and energy constraints. The experimental results demonstrate that our technique is able

to produce schedules close to optimal solution with reasonable execution time on real benchmarks.

### 1.4 Dissertation Organization

This dissertation is organized as follows. Chapter 2 introduces relevant existing research works. Chapter 3 and Chapter 4 describe proposed directed test generation for the functional validation of multicore architectures. Chapter 5 discusses proposed test generation approaches for transition coverage in cache coherence protocols. Chapter 6 describes our scalable directed test generation approach for HDL designs. Chapter 7 describes our schedulability validation approaches under energy and temperature constraints. Chapter 8 presents our schedulability validation technique for multicore processors. Chapter 9 concludes this dissertation.

# CHAPTER 2 RELATED WORK

This chapter surveys existing system-level validation techniques. For ease of presentation, we have divided the existing approaches into three categories. First, we describe the test generation approaches for architecture validation. Next, we discuss existing techniques for validation of cache coherence protocols. Finally, we present techniques for validation of non-functional requirements.

# 2.1 Test Generation for Architecture Validation

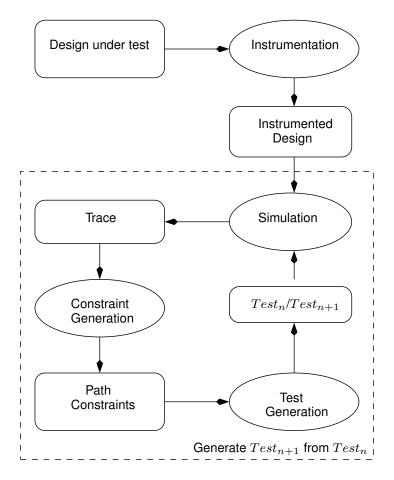

Model checking techniques are promising for functional verification and test generation of complex systems [39, 50, 51, 64]. Figure 2-1 shows the general

Figure 2-1. Directed test generation flow

framework for directed test generation using model checking. In order to create directed tests, the formal model of the design specification and a suitable fault model are provided as input. Then a set of properties are generated for the desired behaviors (faults) that should be activated in the simulation based validation stage. For example, when a graph model of the design and a functional coverage fault model is provided, a coverage-driven property generation can be used. Similarly, in case of circuits with stuck-at fault model, the property will be in the form of G(a = 1) or G(a = 0). Next, a model checker is employed to check whether there exists some states which violate the negated version of the property. If the model checker finds a violation, it reports a counterexample. This counterexample contains a sequence of input information which will drive the system from an initial state to a state that does not satisfy the negated version of the property, or in other words, which satisfies the original property. Therefore, we can use it as a test to activate the corresponding property or behavior during simulation-based validation.

Although model checking is effective for directed test generation, the capacity of the conventional symbolic model checking is usually limited. Bounded model checking (BMC) was proposed to address this problem by checking whether there is a counterexample for the property within a given bound [13] [28]. Given a design D, a safety property p, and a bound k, BMC will unroll the design k times and encode it using the following formula:

$$BMC(M, p, k) = I(s_0) \wedge \bigwedge_{i=0}^{k-1} R(s_i, s_{i+1}) \wedge \bigvee_{i=0}^k \neg p(s_i)$$

(2-1)

where  $I(s_0)$  is the initial state of the system,  $R(s_i, s_{i+1})$  represents the state transition from state  $s_i$  to state  $s_{i+1}$ , and  $p(s_i)$  checks whether property p holds on state  $s_i$ . The formula is then transformed to CNF and checked by a SAT solver. If the SAT solver finds some assignment which makes the CNF true, it implies that the property does not hold at bound k, i.e.,  $M \nvDash_k p$ . Otherwise, if no such assignment is found, we conclude that the property holds up to k, or  $M \vDash_k p$ .

BMC cannot prove the validity of a safety property to hold globally when no counterexample is found within a specific bound, but it is quite effective to falsify a design when the bound is not large. The reason is that SAT solvers usually require less space and time than conventional Binary Decision Diagram (BDD) based model

checkers [65]. Therefore, SAT-based BMC is suitable for directed test generation [64], where a counterexample typically exists within a relatively small bound. To generate the directed test, the negated version of the property is checked by BMC. The SAT solver will find an assignment of all input and state variables, which satisfies Equation (2–1). As a result, we can extract the assignment sequence of input variables and use it as a test to activate the desired property in the system.

A great deal of work has been done to reduce the SAT solving time during BMC [22–25, 43, 52, 79, 91]. The basic idea is to exploit the regularity of the SAT instances between different bounds. For example, incremental SAT solvers [43, 91] reduce the solving time by employing the previously learned conflict clauses. Generated conflict clauses are kept in the database as long as the clauses which led to the conflicts are not removed. Strichman [79] proposed that if a conflict clause is deduced only from the transition part of a SAT instance, it can be safely forwarded to all instances with larger bounds, because the transition part of the design will still be in the SAT instance when we unroll the design for more times. Besides, the learned conflict clauses can also be replicated across different time steps. However, the existing approaches did not exploit the symmetric structure within the same time step. *In directed test generation for multicore architectures, same knowledge about the core structure needs to be re-discovered for each core independently, which can lead to significant wastage of computational power.*

When BMC is applied in circuits, Kuehlmann [53] proposed that the unfolded transition relation can be simplified by merging vertices that are functionally equivalent under given input constraints. In this way, the complexity of transition relation is greatly reduced. Since this technique is based on the AIG representation of logic designs, it is difficult to use for accelerating the solving process of CNF instances, which are directly created from high level specifications. Functional validation based on high level specification is very effective in many scenarios. For example, Bhadra et al. [45] used

executable specification to validate multiprocessor systems-on-chip designs. Chen et al. [22] proposed directed test generation based on high level specification. To accelerate the test generation process, conflict clauses learned during checking of one property are forwarded to speed up the SAT solving process of other related properties, although the bound is required as an input. Similarly, the simultaneous SAT solver [49] enabled the learned clauses to be reused by properties. Decision ordering was also studied in [23] to reduce the SAT solving time. *These approaches did not take the advantage of structural symmetry in multicore architectures.*

When SAT instance contains symmetric structure, symmetry breaking predicate [3, 5, 30, 62, 80] can be used to speed up the SAT solving by confining the search to non-symmetric regions of the space. By adding symmetry breaking predicates to the SAT instance, the SAT solver is restricted to find the satisfying assignments of only one representative member in a symmetric set. *However, this approach cannot effectively accelerate the directed test generation for multicore processors, because the properties for test generation are usually not symmetric with respect to each core.* Thus, the symmetric regions in the entire space are usually small despite the fact that the structure of each core is identical. Biere et al. [14] proposed that each component can be solved individually to accelerate the solving process. *However, the symmetric structure is not used at the same time for further speedup.*

During the validation process, it is also very important to generate assertions effectively. One important work in this direction is GoldMine [81], which automatically uses data mining and formal verification to generate assertions for real hardware designs. Using the simulation trace of RTL designs, GoldMine employs decision tree based supervised learning algorithms to mine potential assertions from the simulation data. Liu et al. [54] also proposed a methodology, which utilizes GoldMine to achieve coverage closure during design validation. Once the assertion is generated, automatic test generation approaches can be employed to generate the tests, which can be used

to activate the desired behavior of the system. For example, test generation tools based on interleaved concrete and symbolic execution, such as DART [40], CUTE [72], and Apollo [7], are promising in capturing important bugs in large software systems. STAR [55] and HYBRO [56] are proposed to generate tests by combining static and dynamic analysis for hardware validation. Due to the effective utilization of the CFG, HYBRO [56] demonstrated remarkable improvement over previous path-based test generation technique [55]. However, HYBRO cannot be applied on real-life designs containing dynamic array references.

#### 2.2 Validation of Cache Coherence Protocols

Verification of cache coherence protocols for multicore and multiprocessor systems has been widely studied in both academia and industry. Existing studies can be broadly grouped into two categories: formal verification [27, 33, 36] and simulation based validation [2, 83, 93]. Formal methods using model checking can prove mathematically whether the description of certain cache coherence protocol violates the required property. For example, Mur $\varphi$  [33] was designed and used to verify various cache coherence protocols based on explicit model checking. Counter-example guided refinement [27] is employed to verify complex protocols with multilevel caches. Besides, symbolic model checking tools are also developed for coherence verification. For example, Emerson et al. [36] investigated the verification problem with parameterized cache coherence protocol using BDDs. Although formal methods can guarantee the correctness of a design, they usually require that the design should be described in certain input languages. As a result, model checking usually cannot be applied to implementations directly.

Simulation based approaches, on the other hand, are able to handle designs at different abstraction levels and therefore more widely used in practice. For example, Wood et al. [93] used random tests to verify the memory subsystem of SPUR machine. Successive loads and stores to the same location are employed as test template to

expose possible errors. Genesys Pro test generator [2] from IBM extended this direction with more complex and sophisticated test templates. To reduce the search space, Abts et al. [1] introduced space pruning technique during their verification of the Cray processor. Wagner et al. [83] designed the MCjammer tool which can get higher state coverage than normal constrained random tests. Existing random test generation tools are proven to be effective to discover potential bugs. However, due to their random nature, it is very hard to achieve full state and transition coverage in a reasonable time. Since an uncovered transition can only be visited by taking a unique action at a particular state, it may not be feasible for a random test generator to eventually cover all possible states and transitions. To address this problem, some random testers are equipped with small amount of memory, so that the future search can be guided to the uncovered regions. Unfortunately, unless the memory is large enough to hold the entire state space, it is still quite hard to achieve full coverage by such guided random testing.

### 2.3 Task Schedulability under Constraints

Energy-aware scheduling techniques for real-time systems have been widely studied to reduce energy consumption. While several works employed dynamic cache reconfiguration [87] [85], most of them are based on Dynamic Voltage Scaling (DVS). Aydin et al. [9] addressed both static and dynamic slack allocation problems for periodic task sets, while Shin et al. [73] also considered aperiodic tasks. Jejurikar et al. focused on energy-aware scheduling for non-preemptive task sets [47] and leakage power minimization [48]. Zhong et al. [103] solved a system-wide energy minimization problem with consideration of other components. Wang et al. [85] proposed a leakage-aware energy saving technique based on DVS as well as cache reconfiguration. As shown in [100], applying DVS in real-time systems is a NP-hard problem. Optimal and approximation algorithms are given in [103] [100] [86], while other works proposed heuristics. A survey on recent works can be found in [21]. However, these techniques are not aware of controlling the operating temperature.

Temperature-aware scheduling in real-time systems has drawn significant research interests in recent years. Wang et al. [84] introduced a simple reactive DVS scheme aiming at meeting task timing constraints and maintaining processor safe temperature. Zhang et al. [101] proved the NP-hardness of temperature-constrained performance optimization problem in real-time systems and proposed an approximation algorithm. Yuan et al. [97] considered both temperature and leakage power impact in DVS problem for soft real-time systems. Chen et al. [20] explored temperature-aware scheduling for periodic tasks in both uniprocessor and homogeneous multiprocessor DVS-enabled platforms. Liu et al. [57] proposed a design-time thermal optimization framework which is able to solve problem variants energy-aware (EA), temperature -aware (TA) and temperature-constrained energy-aware (TCEA) scheduling in embedded system with task timing constraints. Jayaseelan et al. [46] exploited different task execution orders, in which each task has distinct power profile, to minimize peak temperature. However, none of these techniques solves temperature-constrained and energy-constrained (TCEC) problem. Moreover, they all make certain assumptions on system characteristics that limits their applicability.

Existing research formulated the voltage/frequency assignment problems in different models. For example, Integer Linear Programming (ILP) has been widely applied to many voltage/frequency assignment problems without the temperature constraint [94, 102]. Chantem et al. [19] also used ILP to model scheduling problem with steady-state temperature constraints. Unfortunately, when transient temperature is considered, the full expansion of the temperature constraint introduces a large number of product terms, which prevent us to solve the problem efficiently using ILP solvers. Coskun et al. [29] circumvented this problem using an iterative ILP and thermal simulation approach, although the convergence to the optimal solution is not guaranteed.

Another important modeling technique is timed automata [6]. Norstorm et al. [66] first extended timed automata with the notion of real-time tasks and showed that the traditional schedulability analysis can be transformed to a decidable reachability problem in timed automata, which can be solved using model checking tools. Fersman et al. [37] further generalized this approach with asynchronous processes and preemptive tasks in continuous-time model. However, none of these techniques considered energy or temperature related issues.

There are several studies on Dynamic Power Management (DPM) using formal verification methods for embedded systems [74] and multiprocessor platforms [58]. Shukla et al. [74] provided a preliminary study on evaluating DPM schemes using an off-the-shelf model checker. Lungo et al. [58] tried to incorporate verification of DPM schemes in the early design stage. They showed that tradeoffs can be made between design quality and verification efforts. None of these approaches considers temperature management in such systems. Moreover, they did not account for energy and timing constraints, which are important in real-time embedded systems. Wang et al. [88] discussed the application of timed automata in schedulability problem with both energy and temperature constraints. Nevertheless, due to the capacity limit of model checker, the proposed technique can only be applied to small task sets.

Temperature- or energy-constrained scheduling problems are also related to the multi-constrained path (MCP) problem for Quality of Service (QoS). MCP was extensively studied by network community. For example, Chen et al. [26] designed an approximation algorithm for MCP with two constraints. [76] and [98] studied the efficient heuristics for MCP problems. Xue et al. [96] proposed polynomial time approximation algorithms, which can be applied for more than two constraints. However, since the QoS costs are usually modeled as additive constants, these existing methods cannot be applied directly to solve TCEC problem due to the fact that the computation of the temperature is not additive.

# CHAPTER 3 SYNCHRONIZED GENERATION OF DIRECTED TESTS

Model checking is promising for automatic generation of directed tests [39, 64], because the counterexample of the negated version of a property can be used as a test to activate the property. Existing test generation techniques using SAT-based bounded model checking (BMC) [67] can be divided into two categories based on whether it addresses one property or multiple properties. The first category is applicable for test generation for one design and one property with varying bounds [78, 79]. However, the knowledge obtained are not shared when solving for other properties on the same design. In contrast, the methods in the second category tries to accelerate the test generation for multiple properties with known bounds [63]. They first group similar properties into clusters. Then, the knowledge are shared by all properties in the same cluster. This approach exploit the fact that although each test generation instance is created for a different property, these instances still have a large overlap, because the design remains unchanged. The major drawback of this solution is that it assumes that the bound is known. In general, it is very difficult to determine the bound upfront without actually solving the SAT instance, which limits the applicability of this solution.

In this work [68], we combine the advantages of both approaches by developing a novel BMC based test generation technique for multiple properties of the same design, which enables the reuse of learned knowledge across different bounds as well as across properties in the same cluster. The basic idea of our approach is to *synchronize the solving process of multiple properties for different bounds, so that the utilization of learned knowledge can be maximized*. One may think that solving many SAT instances together can be dramatically complex than solving one instance, and therefore may be impractical. On the contrary, since all these instances are generated by unrolling the same design for several times, we successfully developed a simple but effective approach to significantly reduce the overall SAT solving time by forwarding knowledge among different solving processes. Our experimental results demonstrate an order-of-magnitude reduction in overall test generation time.

The rest of the chapter is organized as follows. Section 3.1 briefly discusses the background on SAT-based BMC. Section 3.2 describes our test generation methodology for multiple properties and bounds. Section 3.3 presents our experimental results. Finally, Section 3.4 concludes this chapter.

#### 3.1 Background

This section briefly describes the basic concepts of existing acceleration techniques for directed test generation using BMC.

#### 3.1.1 Conflict clause forwarding

Many techniques and heuristics are employed in SAT solvers to accelerate the solving process. Modern SAT solvers such as zChaff [38] and GRASP [59] adopt the Davis-Putnam-Logemann-Loveland (DPLL) [31, 32] algorithm and conflict-driven non-chronological backtracking. The basic idea behind these techniques is to save the knowledge learned during resolving current conflict to avoid the same conflict in the future [99]. A conflict occurs, when the current assignment of some variables, through a set of clauses, implies that one variable must be true and false at the same time. In this case, conflict analysis will trace back along the implication relations and find the closest assignment of variables that led to the conflict. We can forbid such assignment from occurring again by adding a carefully designed clause, i.e., conflict clause, to the original CNF. Generally, conflict clauses are only meaningful within the same SAT instance. However, when the set of clauses that led to the conflict clause are shared by multiple SAT instances, we can also forward conflict clauses across instances.

#### 3.1.2 **Property clustering**

Property clustering is another important technique to reduce the total test generation time with BMC. As indicated in Figure 2-1, for a given design and fault model, we first generate a set of properties, which can be used to activate all the faults.

Then, different SAT instances for these properties are solved to obtain the tests. Since sharing of knowledge among similar properties usually reduces the overall solving time, we can cluster properties into different groups and solve all the properties in the same group together.

Although the intention behind property clustering is intuitive, the challenge here is to determine the proper number of clusters and which properties should be in the same cluster. On one extreme, one can group all properties into a single cluster and solve them together. Although this approach maximizes the sharing of knowledge among properties, it also increases the possibility that too many conflict clauses are accumulated in the solver's database, which hampers the overall performance of the SAT solver. On the other extreme, we can also let each cluster have only one property, which is actually the approach adopted by Strichman et al. [79]. In this way, only knowledge relevant to the properties will be explored. However, it is also possible that the same knowledge will be discovered again and again for different properties, which is a significant overhead, when the number of similar properties is large. Therefore, it is desirable to strike a balance between the knowledge sharing and overhead introduced by irrelevant conflict clauses.

Our property clustering approach for designs given in graph models is similar to [63]. The properties are grouped together by their similarity on structural or textual overlap. The properties in the same cluster are describing behaviors of the same functional unit or component. In this way, it is likely that the knowledge or conflict clauses that we obtained during solving one property will be helpful to other properties in the same cluster. For circuits with stuck-at fault model, we perform the clustering of properties based on the cone-of-influence (COI). Output signals with large overlap in their COIs are grouped into the same cluster.

### 3.2 Synchronized Test Generation

Figure 3-1 shows the framework of our synchronized test generation approach. In order to create directed tests, the formal model of the design, a set of properties for the desired behaviors (faults) that should be activated, and the corresponding cluster information are accepted as input. Next, the SAT instances for each property are grouped into different clusters based on their similarity and then solved simultaneously to create the test suite, which can be used to trigger the desired behaviors during simulation-based validation. Algorithm 1 outlines the key steps in our directed test generation framework. The contribution is the synchronized test generation for properties in a cluster, which will be explained in details in Algorithm 2.

Figure 3-1. Synchronized Test Generation

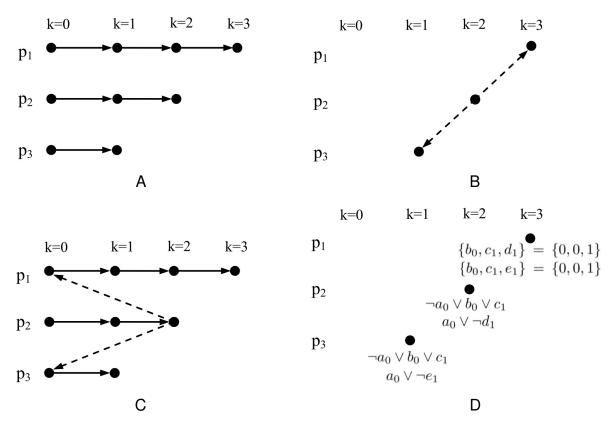

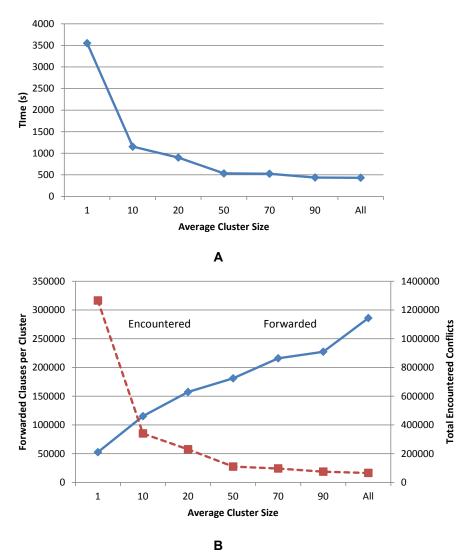

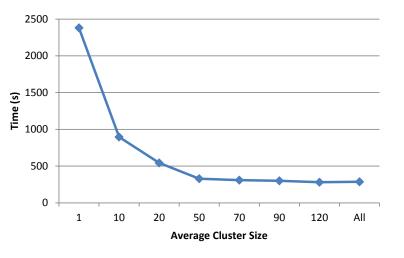

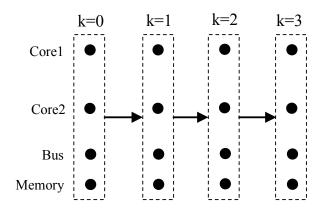

To highlight the contribution of our work, Figure 3-2 compares our approach with two closely related techniques: i) incremental SAT for single property with unknown bound [79] and ii) test generation for multiple properties with known bounds [63]. In this example, there are three properties  $p_1$ ,  $p_2$ , and  $p_3$  with bounds 3, 2, and 1 respectively. We use solid dots to represent different SAT instances and lines to indicate the conflict clause forwarding paths. Strichman et al. [79] solved each property separately, and

| Algorithm 1: Test generation framework       |

|----------------------------------------------|

| Input: i) Design <i>D</i> , ;                |

| ii) Properties P for fault activation ;      |

| Output: Tests for corresponding faults       |

| Cluster similar properties into groups.;     |

| $TestSuite = \emptyset;$                     |

| for each property cluster $PC$ do            |

| Perform Synchronized Test Generation on PC.; |

| Add generated tests into TestSuite.;         |

| end                                          |

| return TestSuite                             |

Figure 3-2. Different incremental SAT solving techniques. A) Strichman [79]. B) Mishra and Chen [63]. C) A naive combination of [79] and [63]. D) Tentative assignment of variables during checking  $p_1$  at k = 3.

passed the knowledge (deduced conflict clauses) "horizontally" within instances for the same property (Figure 3-2A). In contrast, Mishra et al. [63] solved one "base" property first, (e.g.,  $p_2$  in this case), then forward the learned clause "vertically" between other SAT instances for different properties, as shown in Figure 3-2B.

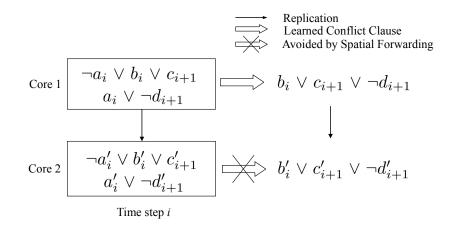

Clearly, it should be profitable if we can appropriately forward conflict clauses "vertically" between properties while solving for each property "horizontally". In this way, the knowledge learned during checking a property for a specific bound can benefit itself with larger bounds as well as across other properties. One intuitive way to combine the two approaches, as shown in Figure 3-2C, is to choose some property as based property ( $p_2$  in Figure 3-2C), check this property for different bounds, and then forward the learned conflict clauses to other SAT instances for other properties. Unfortunately, this naive combination has three problems. First, it is very hard to choose the base property, that should yield a large number of conflict clauses which can be shared by other properties. Unlike [63], where each property has only one SAT instance, we do not know how many SAT instances we have to solve. As a result, it is impossible to apply the clustering technique proposed in [63], to determine the base property. Secondly, even if we correctly find the optimal base property, it is still difficult to choose the suitable bound of the receiving property to forward clauses, because SAT instances with inappropriate bounds may be solved trivially. Moreover, the learning during checking non-base properties is wasted. For example, in Figure 3-2D, suppose  $(\neg a_i \lor b_i \lor c_{i+1})$ ,  $(a_i \vee \neg d_{i+1})$  and  $(a_i \vee \neg e_{i+1})$  are clauses within the transition constraint of the system at time step i + 1.

In the SAT solving process of  $p_2$  with bound k = 2, a conflict clause  $(b_0 \lor c_1 \lor \neg d_1)$  is deduced based on  $(\neg a_0 \lor b_0 \lor c_1)$  and  $(a_0 \lor \neg d_1)$  to prevent the assignment  $\{b_0, c_1, d_1\} =$  $\{0, 0, 1\}$ , which will result in a conflict on  $a_0$ . During the solving process of  $p_1$  with bound k = 2, the SAT solver may explore the assignment  $\{b_0, c_1, d_1\} = \{0, 0, 1\}$  if Strichman's approach [79] is employed. Such assignment can be avoided by using [63] (as shown

in Figure 3-2B and Figure 3-2C), because the learned conflict clause  $(b_0 \lor c_1 \lor \neg d_1)$  is forwarded to  $p_1$ .

However, learned clauses are only allowed to be forwarded from the base property  $(p_2 \text{ in this case})$ . The knowledge learned during solving non-base properties will not be reused. As indicated in Figure 3-2D, conflict clause  $(b_0 \lor c_1 \lor \neg e_1)$  is deduced based on  $(\neg a_0 \lor b_0 \lor c_1)$  and  $(a_0 \lor \neg e_1)$  during the solving process of  $p_3$  with bound k = 1. Since  $p_3$  is not a base property, this information will not be reused by  $p_1$ . Therefore, during the solving process of  $p_1$  with bound k = 2, the SAT solver will still try to make the assignment  $\{b_0, c_1, e_1\} = \{0, 0, 1\}$ . When the number of properties is large, this may cause a great waste of computational power, because we have to explore the same search space for many times, if the space is not visited during the solving process of the base property.

Our approach to solve this problem is based on the effective identification of conflict clauses that can be shared by other SAT instances across properties and bounds. In fact, for any bound  $k_0 \ge 0$ , all SAT instances generated during BMC (Equation 2–1) with  $k \ge k_0$  clearly share the transition clauses  $I(s_0) \land \bigwedge_{i=0}^{k_0-1} R(s_i, s_{i+1})$ , although their property terms  $\bigvee_{i=0}^k \neg p(s_i)$  are different. This observation implies that all conflict causes deduced based on these common clauses during solving process of any SAT instance can be forwarded to any other SAT instances with  $k \ge k_0$ , because all of them have the same set of clauses that led to the conflict clause. Therefore, if we check all properties together for k = 0, 1, 2, ..., i.e., "synchronously", all conflict clauses can be safely shared by all subsequent SAT instances.

Algorithm 2 outlines our synchronized test generation method for clustered properties. It accepts each property cluster and the design of the system as input and produces corresponding tests. As indicated before, this algorithm will check all properties synchronously for each bound. In each iteration, we first generate the transition clause set  $CS_T^k$  (corresponding to  $I(s_0) \wedge \bigwedge_{i=0}^{k-1} R(s_i, s_{i+1})$ ) using BMC(D,true,k),

Algorithm 2: Synchronized Test Generation For Properties in a Cluster

```

Input: i) Design D, ;

ii) Properties P, ;

iii) Maximum bound K_{max}

Output: Test Set TS

Bound k \leftarrow 0;

Common Conflict Clause Set CCS \leftarrow \emptyset;

TS \longleftarrow \emptyset;

while P \neq \emptyset and k \leq K_{max} do

Clause Set CS_T^k \leftarrow BMC(D, true, k);

for p \in P do

Clause Set CS_p^k \longleftarrow BMC(D, p, k);

Step1: In CS_n^k, mark all clauses that also exist in CS_T^k;

Step2: (ConflictC, test_p) \leftarrow SAT(CCS \cup CS_p^k);

Step3: CCS \leftarrow CCS \cup CheckMark (ConflictC);

if test_p \neq null then

remove p from P;

TS \longleftarrow TS \bigcup test_p;

end

end

k \leftarrow k+1;

end

return TS

```

then randomly choose a property p from the property set P, and create its own clause set  $CS_p^k$  (corresponding to  $I(s_0) \wedge \bigwedge_{i=0}^{k-1} R(s_i, s_{i+1}) \wedge \bigvee_{i=0}^k \neg p(s_i)$ ). Next, we perform following 3 steps.

- 1. Mark all clauses in  $CS_p^k$  which are also in  $CS_T^k$ . Since  $CS_T^k$  remains same for all properties at k, this step can be implemented efficiently by table lookup, as described in Section 3.2.2.

- 2. Use a SAT solver to solve the CNF formula  $CCS \bigcup CS_p^k$ , which contains not only  $CS_p^k$ , but also all previously learned conflict clauses in CCS.

- 3. For new conflict clauses *ConflictC* learned by SAT solver, merge the clauses deduced purely by marked clauses into *CCS*. This step is similar to the isolation technique proposed in [78] and [63].

If the satisfied assignment, or a counterexample  $test_p$  is found in step 2, we record

it in test set TS and remove p from P. This process repeats until tests for all properties

are found or the maximum bound  $K_{max}$  is reached. Finally, the algorithm returns all generated tests.

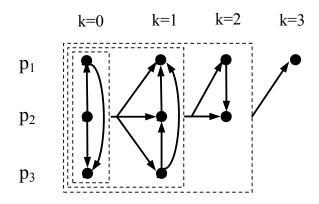

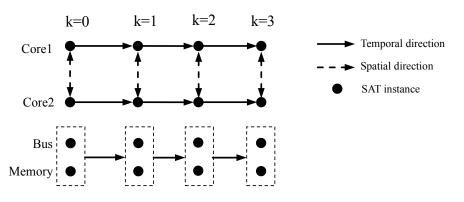

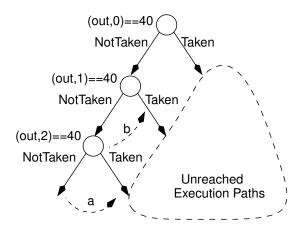

Figure 3-3. Synchronized test generation for multiple properties

We use the same example in Figure 3-2 to illustrate the flow of Algorithm 2. The clause forwarding path are shown in Figure 3-3. In the first iteration for k = 0, suppose we randomly pick  $p_2$  from the property set. At the beginning, the common conflict clause set CCS is empty. Thus,  $p_2$  is solved directly. Since the bound of  $p_2$  is 2, the SAT instance is not satisfiable and no test is generated. However, all conflict clauses deduced based on clauses in  $CS_T^0$  are now recorded in CCS, and will be used to accelerate the solving process of both  $p_1$  and  $p_3$  at bound 0. Similarly, the conflict clauses generated during solving  $p_1$  at k = 0 will be used to speed up  $p_3$  at k = 0(assumes  $p_3$  is solved last). In the next iteration, all instances will be solved with the help of conflict clauses learned by all three SAT instances at k = 0, because all conflict clauses are recorded in CCS. Eventually, three tests will be generated at bound 3, 2, and 1 for  $p_1$ ,  $p_2$  and  $p_3$  respectively. In the case of Figure 3-2D, since both  $(\neg a_0 \lor b_0 \lor c_1)$ ,  $(a_0 \vee \neg d_1)$  and  $(a_0 \vee \neg e_1)$  are clauses from the transition constraint of the system, both  $(b_0 \lor c_1 \lor \neg d_1)$  and  $(b_0 \lor c_1 \lor \neg e_1)$  will be recorded in *CCS* based on Algorithm 2. Therefore, during the solving process of  $p_1$  with bound k = 2, the SAT solver will skip the assignment  $\{b_0, c_1, d_1\} = \{0, 0, 1\}$  and  $\{b_0, c_1, d_1\} = \{0, 0, 1\}$ . In this way, the unnecessary waste of time is avoided.

Note that our algorithm does not require the SAT instances to be preprocessed using Cone-Of-Influence (COI) optimization as in [79] and [63], because original SAT instances have more overlapped clauses, which are effectively exploited by our approach to accelerate the overall solving process. Our experimental results in Section 3.3 show that our approach (without COI) outperforms [79] and [63] that use COI optimization.

In the remainder of this section, we prove the correctness of our approach and discuss the implementation details of our synchronized test generation algorithm.

### 3.2.1 Correctness of the Proposed Approach

To show the correctness of our test generation approach, we need to show that in Algorithm 2, solving  $CCS \bigcup CS_p^k$  is equivalent to solving  $CS_p^k$ . Formally, let  $\varphi_p^k$  and  $\psi$  be the CNF formulae formed by clause set  $CS_p^k$  and CCS respectively, we need to prove that  $\varphi_p^k$  is satisfiable iff  $\varphi_p^k \wedge \psi$  is satisfiable using the following lemma.

Lemma 1.  $\varphi_p^k \vdash \psi$  for all  $p \in P$  and  $k \ge 0$ .

*Proof.* Let  $\varphi_T^k$  be the CNF formula formed by  $CS_T^k$ . We first show that

$$\varphi_T^k \vdash \psi$$

(3–1)