UNIVERSITY OF CALIFORNIA, IRVINE

## Specification-driven Validation of Programmable Embedded Systems

DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in Information and Computer Science

by

## Prabhat Kumar Mishra

Dissertation Committee: Professor Nikil Dutt, Chair Professor Rajesh Gupta Professor Alex Nicolau

2004

© 2004 Prabhat Kumar Mishra

The dissertation of Prabhat Kumar Mishra is approved and is acceptable in quality and form for publication on microfilm:

Committee Chair

University of California, Irvine2004

To my parents and my wife.

## Contents

| Li       | List of Figures v          |         |                                            |     |  |  |

|----------|----------------------------|---------|--------------------------------------------|-----|--|--|

| Li       | List of Tables ix          |         |                                            |     |  |  |

| Ac       | cknov                      | wledgn  | nents                                      | x   |  |  |

| Cı       | irric                      | ulum V  | Vitae                                      | xi  |  |  |

| Al       | ostra                      | ct of t | he Dissertation                            | xii |  |  |

| 1        | Intr                       | oducti  | on                                         | 1   |  |  |

|          | 1.1                        | Tradit  | ional Bottom-Up Validation Flow            | 2   |  |  |

|          | 1.2                        | Propos  | sed Top-Down Validation Methodology        | 4   |  |  |

|          | 1.3                        | Thesis  | Contributions                              | 5   |  |  |

|          | 1.4                        | Thesis  | Organization                               | 8   |  |  |

| <b>2</b> | Architecture Specification |         |                                            |     |  |  |

|          | 2.1                        | Archit  | ecture Description Languages               | 9   |  |  |

|          |                            | 2.1.1   | Behavioral ADLs                            | 11  |  |  |

|          |                            | 2.1.2   | Structural ADLs                            | 11  |  |  |

|          |                            | 2.1.3   | Mixed ADLs                                 | 12  |  |  |

|          | 2.2                        | Specifi | cation using EXPRESSION ADL                | 13  |  |  |

|          |                            | 2.2.1   | Processor Specification                    | 15  |  |  |

|          |                            | 2.2.2   | Coprocessor Specification                  | 16  |  |  |

|          |                            | 2.2.3   | Memory Subsystem Specification             | 18  |  |  |

|          |                            | 2.2.4   | Specification of Interrupts and Exceptions | 19  |  |  |

|          | 2.3                        | Chapt   | er Summary                                 | 21  |  |  |

| 3        | Vali                       | dation  | of Specification                           | 23  |  |  |

|          | 3.1                        | Valida  | tion of Static Behavior                    | 24  |  |  |

|          |                            | 3.1.1   | Graph-based Modeling of Pipelines          | 25  |  |  |

|          |                            | 3.1.2   | Validation of Pipeline Specifications      | 29  |  |  |

|          |     | 3.1.3    | Experiments                                   | 42  |

|----------|-----|----------|-----------------------------------------------|-----|

|          | 3.2 | Validat  | tion of Dynamic Behavior                      | 46  |

|          |     | 3.2.1    | FSM-based Modeling of Processor Pipelines     | 47  |

|          |     | 3.2.2    | Validation of Dynamic Properties              | 52  |

|          |     | 3.2.3    | A Case Study                                  | 58  |

|          | 3.3 | Chapte   | er Summary                                    | 60  |

| 4        | Mo  | del Gei  | neration using Functional Abstraction         | 62  |

|          | 4.1 | Survey   | of Contemporary Architectures                 | 63  |

|          |     | 4.1.1    | Summary of Architectures Studied              | 63  |

|          |     | 4.1.2    | Similarities and Differences                  | 64  |

|          | 4.2 | Function | onal Abstraction                              | 67  |

|          |     | 4.2.1    | Structure of a Generic Processor              | 67  |

|          |     | 4.2.2    | Behavior of a Generic Processor               | 72  |

|          |     | 4.2.3    | Structure of a Generic Memory Subsystem       | 72  |

|          |     | 4.2.4    | Generic Controller                            | 73  |

|          |     | 4.2.5    | Interrupts and Exceptions                     | 74  |

|          | 4.3 | Referen  | nce Model Generation                          | 75  |

|          | 4.4 | Design   | Space Exploration                             | 79  |

|          |     | 4.4.1    | Simulator Generation and Exploration          | 79  |

|          |     | 4.4.2    | Hardware Generation and Exploration           | 90  |

|          | 4.5 | Chapte   | er Summary                                    | 94  |

| <b>5</b> | Spe | cificati | on-driven Validation                          | 96  |

|          | 5.1 | Design   | Validation                                    | 98  |

|          |     | 5.1.1    | Property Checking using Symbolic Simulation   | 99  |

|          |     | 5.1.2    | Equivalence Checking                          | 101 |

|          | 5.2 | Experi   | ments                                         | 103 |

|          |     | 5.2.1    | Property Checking of a Memory Management Unit | 103 |

|          |     | 5.2.2    | Equivalence Checking of the DLX Architecture  | 106 |

|          | 5.3 | Chapte   | er Summary                                    | 107 |

| 6        | Fun | ctional  | Test Generation                               | 109 |

|          | 6.1 | Test G   | eneration using Model Checking                | 109 |

|          |     | 6.1.1    | Test Generation Methodology                   | 110 |

|          |     | 6.1.2    | A Case Study                                  | 113 |

|          | 6.2 | Function | onal Coverage driven Test Generation          | 117 |

|          |     | 6.2.1    | Functional Fault Models                       | 118 |

|          |     | 6.2.2    | Functional Coverage Estimation                | 121 |

|          |     | 6.2.3    | Test Generation Techniques                    | 121 |

|          |     |          | -                                             |     |

|          |     | 6.2.4    | A Case Study                                  | 126 |

| <b>7</b> | Con   | clusions and Future Work   | 132 |

|----------|-------|----------------------------|-----|

|          | 7.1   | Conclusions                | 132 |

|          | 7.2   | Future Research Directions | 134 |

| Bi       | bliog | raphy                      | 137 |

# List of Figures

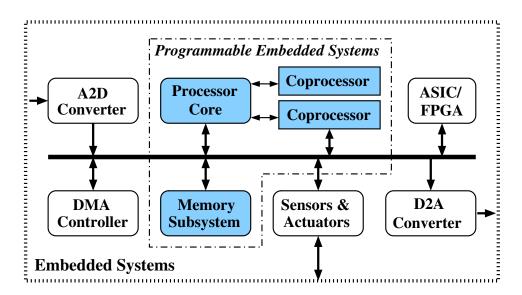

| 1.1  | An example embedded system                                                       | 2  |

|------|----------------------------------------------------------------------------------|----|

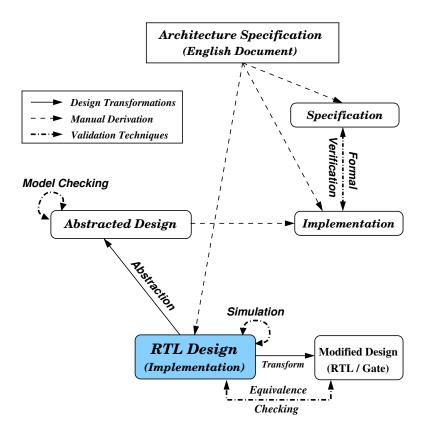

| 1.2  | Bottom-up validation flow for programmable embedded systems $\ . \ .$            | 3  |

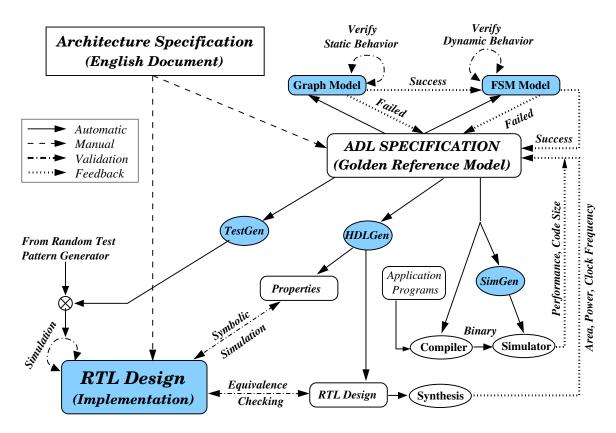

| 1.3  | Proposed specification-driven validation methodology $\ldots \ldots \ldots$      | 5  |

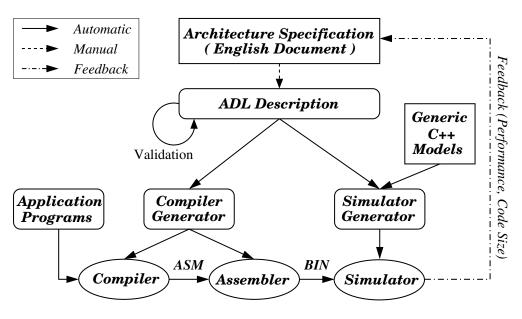

| 2.1  | ADL-driven design space exploration                                              | 10 |

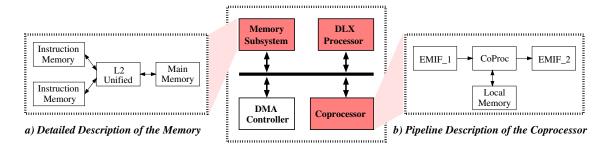

| 2.2  | Block level description of an example architecture $\ldots \ldots \ldots \ldots$ | 13 |

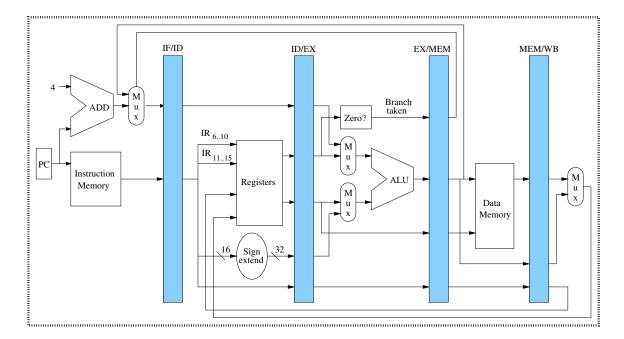

| 2.3  | Pipeline level description of the DLX processor shown in Figure 2.2 $\ .$        | 14 |

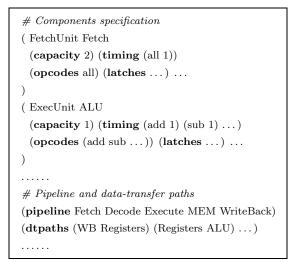

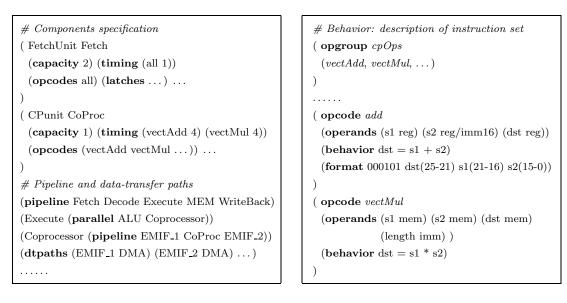

| 2.4  | Processor specification using EXPRESSION ADL                                     | 16 |

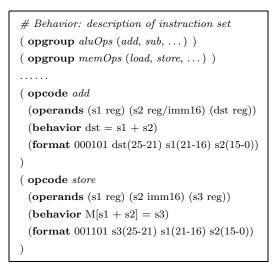

| 2.5  | Coprocessor specification using EXPRESSION ADL                                   | 17 |

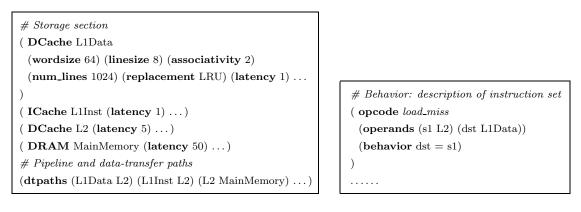

| 2.6  | Memory subsystem specification using EXPRESSION ADL                              | 18 |

| 2.7  | Specification of division_by_zero exception                                      | 19 |

| 2.8  | Specification of illegal_slot_instruction exception                              | 20 |

| 2.9  | Specification of machine_reset exception                                         | 20 |

| 2.10 | Specification of interrupts                                                      | 21 |

| 3.1  | Validation of pipeline specifications                                            | 25 |

| 3.2  | An example architecture                                                          | 26 |

| 3.3  | A fragment of the behavior graph                                                 | 28 |

| 3.4  | An example processor with false pipeline paths                                   | 32 |

| 3.5  | An example processor with false data-transfer paths                              | 35 |

| 3.6  | The DLX architecture                                                             | 43 |

| 3.7  | ADL driven validation of pipeline specifications                                 | 46 |

| 3.8  | A fragment of the processor pipeline                                             | 48 |

| 3.9  | Automatic validation frameworks                                    | 57  |

|------|--------------------------------------------------------------------|-----|

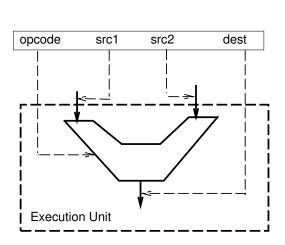

| 4.1  | A fetch unit example                                               | 68  |

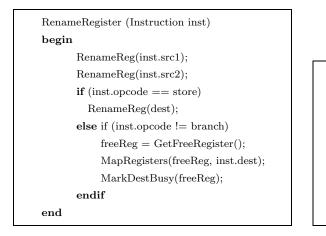

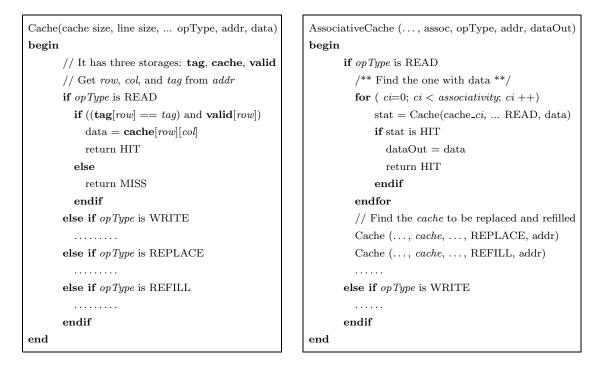

| 4.2  | Modeling of RenameRegister function using sub-functions            | 69  |

| 4.3  | Modeling of MAC operation                                          | 72  |

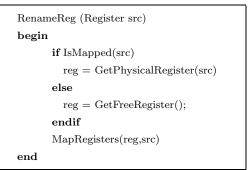

| 4.4  | Modeling of associative cache function using sub-functions         | 73  |

| 4.5  | Examples of distributed and centralized controllers                | 74  |

| 4.6  | Mapping between <i>MACcc</i> and generic instructions              | 77  |

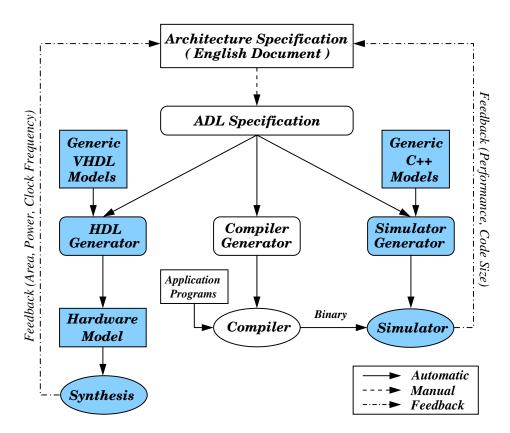

| 4.7  | Simulation model generation for the DLX architecture               | 78  |

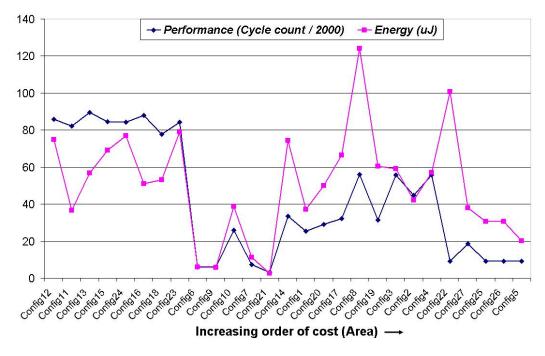

| 4.8  | Architecture exploration framework                                 | 80  |

| 4.9  | Cycle counts for different graduation styles                       | 81  |

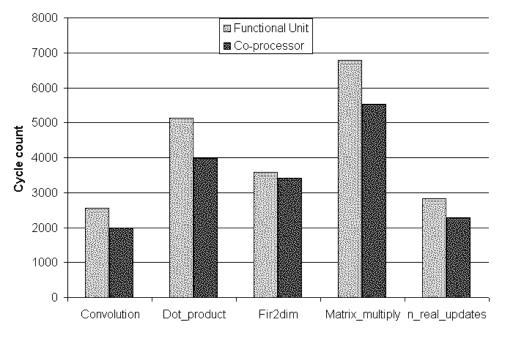

| 4.10 | Functional unit vs. coprocessor                                    | 82  |

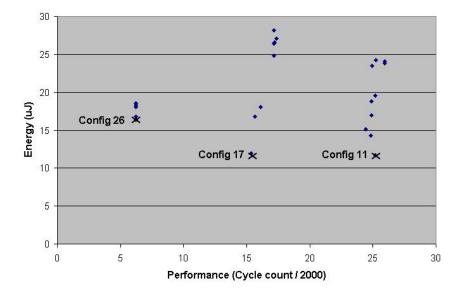

| 4.11 | Memory exploration results for GSR                                 | 87  |

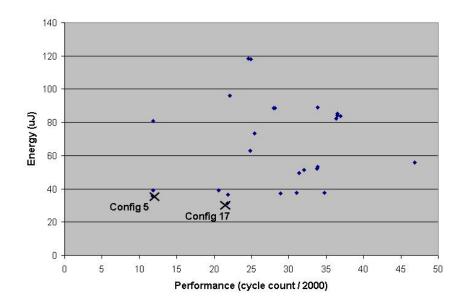

| 4.12 | Energy performance tradeoff for Compress                           | 88  |

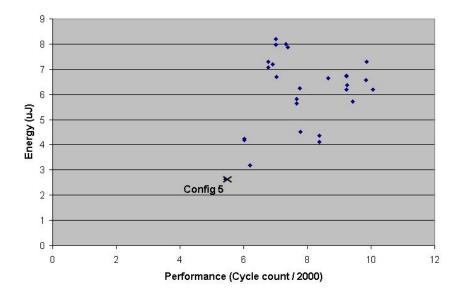

| 4.13 | Energy performance tradeoff for MatMult                            | 89  |

| 4.14 | Energy performance tradeoff for Laplace                            | 90  |

| 4.15 | The application program                                            | 91  |

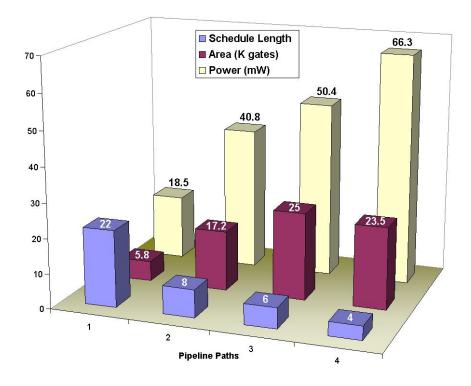

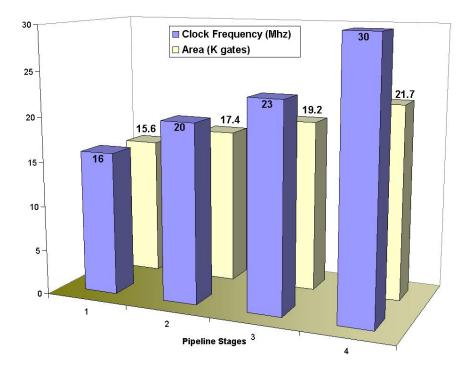

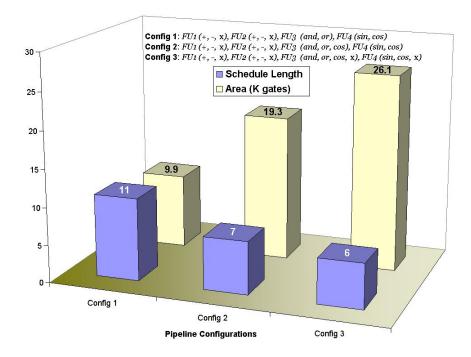

| 4.16 | Pipeline path exploration                                          | 92  |

| 4.17 | Pipeline stage exploration                                         | 93  |

| 4.18 | Instruction-set exploration                                        | 94  |

| 5.1  | Top-down validation methodology                                    | 97  |

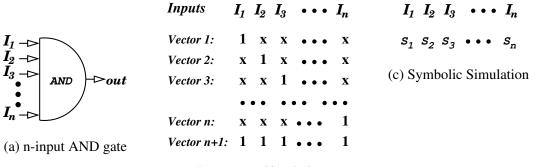

| 5.2  | Test vectors for validation of an AND gate                         | 99  |

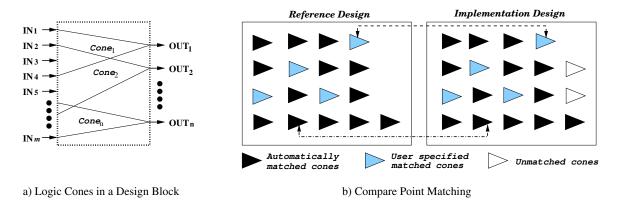

| 5.3  | Compare point matching between reference and implementation design | 102 |

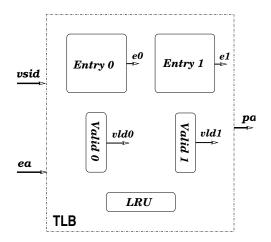

| 5.4  | TLB block diagram                                                  | 105 |

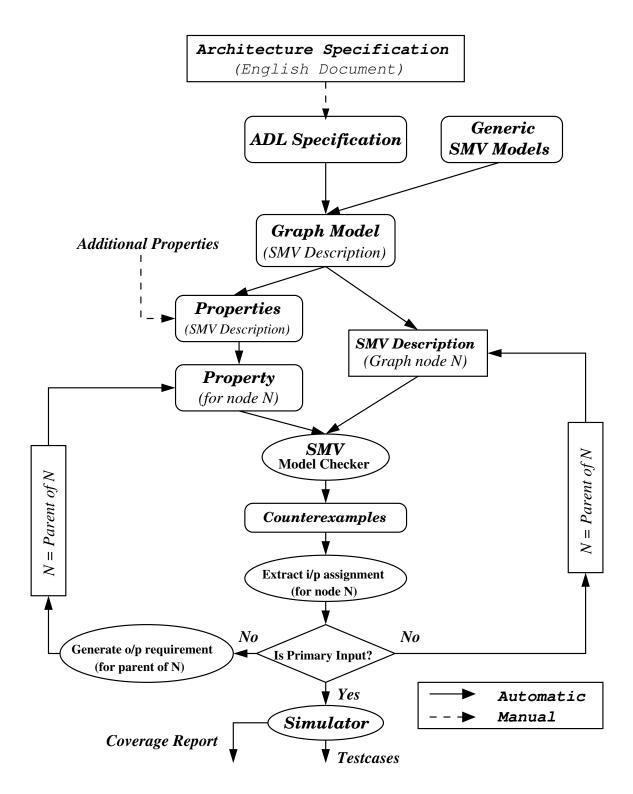

| 6.1  | Test program generation methodology                                | 111 |

| 6.2  | A fragment of the DLX architecture                                 | 115 |

# List of Tables

| 3.1 | Specification validation time for different architectures                                                                             | 42  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Summary of property violations during DSE                                                                                             | 45  |

| 3.3 | Validation of in-order execution by two frameworks $\ . \ . \ . \ . \ .$                                                              | 60  |

| 4.1 | Processor-memory features of different architectures. R4K: MIPS R4000,<br>SA: StrongArm, 56K: Motorola 56K, c5x: TI C5x, c6x: TI C6x, |     |

|     | MA: MAP1000A, SC: Starcore, R10: MIPS R10000, MP: Motorola                                                                            |     |

|     | MPC7450, U3: SUN UltraSparc IIi, $\alpha 64$ : Alpha 21364, IA64: Intel                                                               |     |

|     | IA-64                                                                                                                                 | 65  |

| 4.2 | A list of common sub-functions                                                                                                        | 70  |

| 4.3 | Benchmarks                                                                                                                            | 84  |

| 4.4 | The memory subsystem configurations                                                                                                   | 85  |

| 5.1 | Validation of the DLX implementation using equivalence checking $\ .$ .                                                               | 107 |

| 6.1 | Number of test programs in different categories                                                                                       | 114 |

| 6.2 | Reduced number of test programs                                                                                                       | 114 |

| 6.3 | Test programs for validation of DLX architecture                                                                                      | 129 |

| 6.4 | Test programs for validation of LEON2 processor                                                                                       | 130 |

## Acknowledgments

First of all, I would like to thank my advisor Prof. Nikil Dutt for his guidance and support throughout my graduate studies. Without the numerous discussions and brainstorms with him, the results presented in this thesis would never have existed. I am grateful to Prof. Alex Nicolau for his guidance and encouragement during last four years. I would also like to thank Prof. Rajesh Gupta for his valuable comments and suggestions on my research.

This thesis is the result of many collaborations. I would like to acknowledge the contributions of Jonas Astrom, Dr. Peter Grun, Ashok Halambi, Arun Kejariwal, Mahesh Mamidipaka, Dr. Frederic Rousseau, Prof. Sandeep Shukla, and Prof. Hi-royuki Tomiyama. I would also like to thank Dr. Magdy Abadir and Dr. Narayanan Krishnamurthy for their help in my research work.

I am thankful to many people in the Center for Embedded Computer Systems (CECS) for making my journey a memorable one. In particular, I would like to thank Melanie Sanders for her help and understanding throughout my graduate life. I would also like to thank all my colleagues in CECS, including Ana Azevedo, Sudarshan Banerjee, Nikhil Bansal, Partha Biswas, Radu Cornea, Paolo DAlberto, Sumit Gupta, Ilya Issenin, Dan Nicolaescu, Sudeep Pasricha, Mehrdad Reshadi, Nick Savoiu, Srikanth Srinivasan, and Aviral Srivastava.

Last but not least, I am grateful to my parents and my wife for their love, encouragement, and understanding. It would be impossible for me to express my gratitude towards them in mere words. I dedicate this thesis to them.

## Curriculum Vitae

### Prabhat Mishra

### Education

2004 Ph.D. in Computer Science, University of California, Irvine, USA

1996 M.Tech. in Computer Science, Indian Institute of Technology, Kharagpur

1994 B.E. in Computer Science, Jadavpur University, Calcutta, India

### **Research and Work Experience**

| 1999 - 2004 | Graduate Researcher      | University of California, Irvine, USA |

|-------------|--------------------------|---------------------------------------|

| 2001, 2002  | Summer Research Intern   | Somerset Design Center, Motorola, USA |

| 2000        | Summer Research Intern   | IA-64 Performance Group, Intel, USA   |

| 1998 - 1999 | Senior R&D Engineer      | Synopsys, Bangalore, India            |

| 1997 - 1998 | Senior Software Engineer | Sasken, Bangalore, India              |

| 1996 - 1997 | Software Design Engineer | Texas Instruments, Bangalore, India   |

### Selected Publications

- 1. P. Mishra and N. Dutt, "Modeling and Validation of Pipeline Specifications", ACM Transactions on Embedded Computing Systems (TECS), 3(1), 114–139, 2004.

- P. Mishra, M. Mamidipaka, and N. Dutt, "Processor-Memory Co-Exploration using an Architecture Description Language", ACM TECS, 3(1), 140–162, 2004.

- P. Mishra, N. Dutt, and H. Tomiyama, "Towards Automatic Validation of Dynamic Behavior in Pipelined Processor Specifications", Kluwer Design Automation for Embedded Systems (DAES), 8(2/3), pages 249-265, 2003.

- 4. P. Mishra, N. Dutt, N. Krishnamurthy, and M. Abadir, "A Top-Down Methodology for Validation of Microprocessors", IEEE Design & Test of Computers, 2004.

- 5. P. Mishra and N. Dutt, "Graph-based Functional Test Program Generation for Pipelined Processors", Design Automation and Test in Europe (DATE), 2004.

- 6. P. Mishra, A. Kejariwal, and N. Dutt, "Synthesis-driven Exploration of Pipelined Embedded Processors", International Conference on VLSI Design, 921–926, 2004.

- M. Reshadi, P. Mishra, and N. Dutt, "Instruction Set Compiled Simulation: A Technique for Fast and Flexible Instruction Set Simulation", Design Automation Conference (DAC), 758–763, 2003.

- 8. M. Reshadi, N. Bansal, P. Mishra, and N. Dutt, "An Efficient Retargetable Framework for Instruction-Set Simulation", Intl. Symposium on Hardware/Software Codesign and System Synthesis (CODES+ISSS), 13-18, 2003. Best Paper Award

## Abstract of the Dissertation

Specification-driven Validation of Programmable Embedded Systems

by

Prabhat Kumar Mishra Doctor of Philosophy in Information and Computer Science University of California, Irvine, 2004 Professor Nikil Dutt, Chair

Validation of programmable embedded systems, consisting of processor cores, coprocessors, and memory subsystems, is one of the major bottleneck in current Systemon-Chip (SOC) design methodology. One of the most important problems in validation of such systems is the lack of a golden reference model. As a result, many existing validation techniques employ a bottom-up approach to design verification, where the functionality of an existing architecture is, in essence, reverse-engineered from its implementation. This thesis presents a top-down validation methodology that complements the existing bottom-up approaches. It leverages the system architect's knowledge about the behavior of the design through architecture specification. We have developed validation techniques to ensure that the static and dynamic behaviors of the specified architecture is well formed. The validated specification is used as a golden reference model. A major challenge in top-down validation methodology is the ability to generate executable models from the specification for a wide variety of programmable architectures. We have developed a functional abstraction technique that enables specification-driven model generation for simulation, hardware generation, and property checking. The generated simulator and hardware models are used for design space exploration of programmable architectures. We have explored two top-down validation scenarios: design validation and test generation. First, the generated hardware is used as a reference model to verify the hand-written implementation using a combination of symbolic simulation and equivalence checking. Second, we have proposed a functional coverage based test generation technique for validation of pipelined processor architectures. The experiments demonstrate the utility of the specification-driven validation methodology for programmable embedded systems.

## Chapter 1

## Introduction

Embedded systems run the computing devices hidden inside a vast array of everyday products and appliances such as cell phones, toys, handheld PDAs, cameras, and microwave ovens. Cars are full of them, as are airplanes, satellites, and advanced military and medical equipments. As applications grow increasingly complex, so do the complexities of the embedded computing devices. Figure 1.1 shows an example embedded system, consisting of programmable components including processor cores, coprocessors and a memory subsystem. The memory subsystem contains memory components such as cache hierarchies and scratch-pad SRAM. Depending on the application domain, the embedded system can have application specific hardwares, interfaces, controllers, and peripherals. In this thesis, we refer to the programmable components, consisting of the processor core, coprocessors, and memory subsystem, as *programmable embedded systems*. We also refer to them as programmable architectures.

Embedded systems are typically designed for dedicated tasks or application domains. The design of such embedded systems often begins with the specification of the application, as well as the definition of the architecture onto which the application is mapped. Validation of programmable embedded systems is one of the most important and complex tasks in embedded systems design. A significant bottleneck in the validation of such systems is the lack of a golden reference model. As a result, many existing approaches employ a bottom-up validation approach by using a combi-

Figure 1.1: An example embedded system

nation of simulation techniques and formal methods. This thesis presents a top-down validation methodology for programmable embedded systems that complements the existing bottom-up techniques. We consider validation of systems with single processor core, coprocessors and memories. Today's embedded systems employ deeply pipelined processor architectures to meet desired system performance. One of the major challenges in validation of such systems is the verification of processor pipelines. The main focus of this thesis is the validation of pipelined processor architectures.

This chapter provides an overview of the problems that will be addressed in the rest of the thesis and outlines a brief summary of the thesis contributions.

### 1.1 Traditional Bottom-Up Validation Flow

Figure 1.2 shows a traditional architecture validation flow. In the current validation methodology, the architect prepares an informal specification of the programmable embedded systems in the form of an English document. The logic designer implements the modules at the register-transfer level (RTL). The *RTL design* is validated using a combination of simulation techniques and formal methods. Simulation is the most widely used form of microprocessor validation using random (or pseudo-random) testcases [1, 12, 35, 77, 91]. Model checking is applied on the highlevel description of the design abstracted from the RTL implementation [23, 37]. Formal verification is performed by describing the system using a formal language [11, 15, 24, 75, 80, 81, 92]. The specification for the formal verification is derived from the architecture description. The implementation for the formal verification can be derived either from the architecture specification or from the abstracted design. The validated *RTL design* is used as a golden reference model for future design modifications. Several design transformations (including synthesis) are applied on the *RTL design*. The modified design is validated against the *RTL design* using equivalence checking.

Figure 1.2: Bottom-up validation flow for programmable embedded systems

The existing processor validation techniques can be divided into two categories depending on the models used for specification and implementation. The techniques in the first category do not verify the actual design implemented by the logic designers. Instead, they verify the implementation written in a formal language that is either abstracted from the actual design or written manually. Hence, this verification does not uncover the bugs in the actual design. The traditional formal verification techniques are in this category. The techniques in the second category are applied on the actual RTL implementation. A significant bottleneck in these techniques is the lack of a golden reference model. As a result, they derive the specification model from the actual implementation by reverse-engineering methods. The simulation based techniques are in this category. The existing techniques employ a bottom-up approach to validation, where the functionality of an existing processor is, in essence, reverse-engineered from its RTL implementation.

### 1.2 Proposed Top-Down Validation Methodology

The validation technique proposed in this thesis is complementary to the existing bottom-up approaches. Our approach leverages the system architect's knowledge about the behavior of the pipelined architecture, through Architecture Description Language (ADL) constructs, and thus allows a top-down approach to architecture validation.

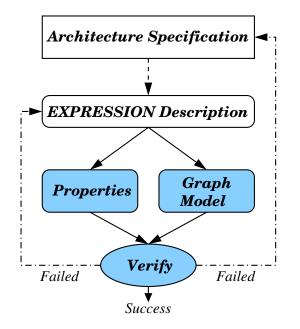

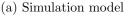

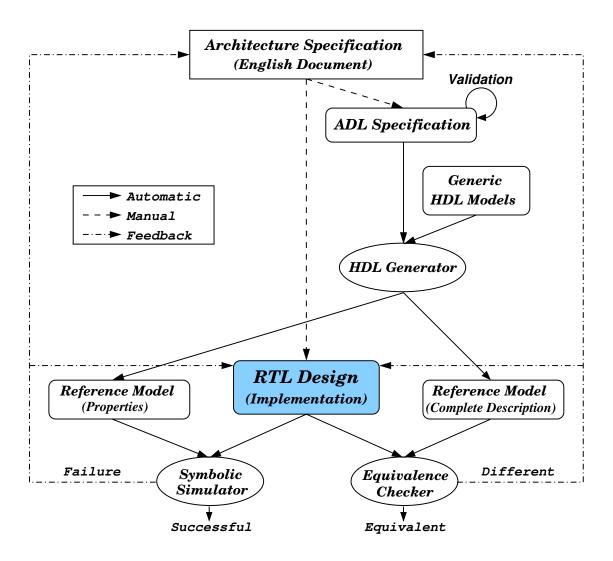

Figure 1.3 shows our top-down validation methodology. The first step is to capture the programmable architecture using the EXPRESSION ADL [20]. The static and dynamic behaviors of the architecture specification are validated to ensure that the specification is well formed. The validated ADL specification is used to generate various executable models including simulator, hardware, and validation models. This thesis explores three top-down validation scenarios using the generated models: *design space exploration*, *design validation*, and *test generation*.

The generated hardware model (by **HDLGen**) and simulator (by **SimGen**) are used for design space exploration of programmable architectures for the given set of application programs under various design constraints such as area, power, and performance. The generated hardware is also used as a reference model for verifying the hand-written implementation (RTL Design) using a combination of symbolic simulation and equivalence checking. Finally, the specification is used to generate

Figure 1.3: Proposed specification-driven validation methodology

functional test programs (by **TestGen**) based on the functional coverage of pipelined architectures. The generated test programs are used to simulate the implementation, and complement the tests generated by the existing techniques such as a random test pattern generator.

### **1.3** Thesis Contributions

This thesis makes two major contributions: validation of the architectural specification, and specification driven validation of programmable embedded systems. We explore three specification-driven validation scenarios: model generation and exploration, top-down design validation, and functional test program generation. Specification validation, model generation, and exploration studies are conducted on programmable architectures with a pipelined processor, coprocessors, and a memory subsystem. However, design validation and test generation techniques are applied mainly on pipelined processor architectures.

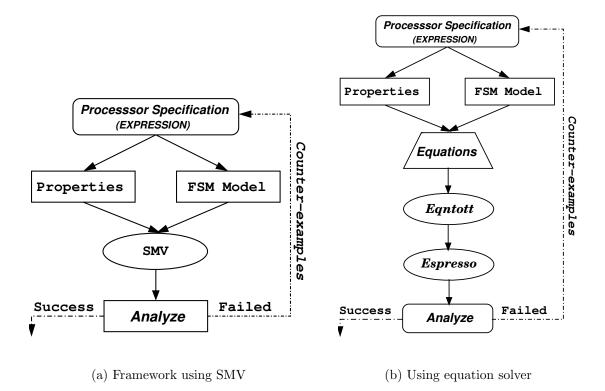

We have developed validation techniques to ensure that the architectural specification is well formed by analyzing the static behavior of the architecture [52, 56, 70]. A novel feature of our approach is the ability to model the pipeline structure and behavior of the processor, coprocessor, as well as the memory subsystem using a graph-based model. Based on this model we present algorithms to ensure that the specification is well formed by verifying several architectural properties, such as connectedness, false pipeline paths, completeness, and finiteness. We have also developed techniques to verify the execution style of the processor architecture specified in the ADL. The dynamic behavior is verified by analyzing the instruction flow in the pipeline using a finite-state machine (FSM) based model to validate several important architectural properties such as determinism and in-order execution in the presence of hazards and multiple exceptions [51, 60, 69]. The validated ADL specification is used as a golden reference model for specification-driven validation of programmable embedded systems.

A major challenge in a top-down validation methodology is the ability to generate executable models from the specification for a wide variety of programmable architectures including RISC (Reduced Instruction Set Computing), DSP (Digital Signal Processing), VLIW (Very Long Instruction Word), and superscalar architectures. We developed a functional abstraction approach by studying the similarities and differences of each architectural feature in various architecture domains. Based on our observations we have defined necessary generic functions, sub-functions, and computational environment needed to capture a wide variety of programmable architectures. Our functional abstraction technique enables generation of models for simulation, hardware generation, and property checking from the ADL specification. We have developed a technique for retargetable simulator generation using functional abstraction [57]. The generated simulators are used for functional validation and design space exploration of programmable architectures [61, 65, 66]. Simulation-based exploration may answer questions concerning the instruction set, the performance of an algorithm and the required size of memory and registers. However, it is necessary to generate hardware model to determine the required silicon area, clock frequency, and power consumption of the specified architectures. We have also developed a technique for specification-driven hardware generation [62, 63]. Our design space exploration results demonstrate the power of reuse in composing architectures using functional abstraction primitives allowing for a reduction in the time for specification, model generation, and exploration. by an order of magnitude.

The generated hardware is also used as a reference model for verifying the handwritten RTL implementation [55]. An important aspect of our methodology is the ability to perform both model (property) checking and equivalence checking depending on the generated reference model. To verify that the implementation satisfies certain properties, our framework generates the intended properties. We use a symbolic simulator to perform property checking. Our framework generates the RTL description of the pipelined processor to enable equivalence checking with the handwritten implementation.

We have developed two specification-driven test generation techniques: model checking based and functional coverage based. The first technique uses a model checker to generate test programs [50, 54]. The processor model is generated from the ADL specification. Properties are generated based on the coverage of the processor pipeline. The generated properties are applied on the processor model using the SMV model checker [28]. The generated counterexamples are converted into test programs consisting of instruction sequences. We have also developed a functional coverage based test generation technique for pipelined architectures [53]. A general graph-theoretic model is developed that can capture the structure and behavior (instruction-set) for a wide variety of pipelined processors. We have proposed a functional fault model that is used to define the functional coverage of pipelined processors. We have also developed test generation procedures that accept the graph model of the architecture as input and generate test programs to detect all the faults in the functional fault model. Our experimental results demonstrate that the number of test programs generated by our approach to obtain a fault coverage is an order of magnitude less than those generated by random or constrained-random test generation techniques.

### 1.4 Thesis Organization

The organization of the thesis is as follows. Chapter 2 surveys the existing ADLs that can be used to specify the programmable architectures. This chapter also presents the EXPRESSION ADL that is used in our validation framework to specify processor, coprocessor, and memory architectures.

Chapter 3 presents the techniques for validating the architecture specification. These techniques verify the static and dynamic behaviors of the specified architecture. The validated specification is used as a reference model in three top-down validation scenarios: model generation and exploration, design validation, and test generation.

The functional abstraction technique is presented in Chapter 4. It enables automatic generation of models for simulation, hardware generation, and validation for a wide variety of programmable architectures. This chapter also presents exploration experiments using the generated simulator and hardware models.

In Chapter 5, the generated hardware is used as a reference model for verifying the hand-written RTL implementation using a combination of symbolic simulation and equivalence checking.

Chapter 6 presents two specification-driven test generation techniques. The first technique enables functional test program generation using model checking. The second technique generates test programs based on functional coverage of the pipelined processor architectures.

Finally, Chapter 7 contains a summary of the thesis and a discussion of future research directions.

## Chapter 2

## **Architecture Specification**

The first step in a top-down validation methodology is to capture the programmable architecture using a specification language. The language should be powerful enough to specify the wide spectrum of contemporary processor, coprocessor, and memory features. On the other hand, the language should be simple enough to allow correlation of the information between the specification and the architecture manual.

This chapter is organized as follows. Section 2.1 introduces the notion of an Architecture Description Language (ADL) and surveys the existing ADLs in terms of their specification capabilities. Section 2.2 describes architecture specification using EXPRESSION ADL [20]. Finally, Section 2.3 summarizes the chapter.

### 2.1 Architecture Description Languages

The phrase Architecture Description Language (ADL) is used in the context of designing both software and hardware architectures. Software ADLs are used for representing and analyzing software architectures ([14], [47]). It captures the behavioral specifications of the components and their interactions that comprise the software architecture. On the other hand, hardware ADLs (such as processor ADLs) capture the structure (hardware components and their connectivity), and the behavior (instruction-set) of processor architectures. In this thesis the term ADL will refer to hardware architecture description language.

Figure 2.1: ADL-driven design space exploration

Traditionally, ADLs are used for early exploration of programmable embedded systems. Embedded systems present a tremendous opportunity to customize designs by exploiting the application behavior. ADLs enable exploration of programmable architectures for a given set of application programs under the design constraints such as area, power and performance.

Figure 2.1 shows a traditional ADL-driven exploration flow. The ADL is used to specify the processor, coprocessor and memory architectures. The software toolkit including the compiler, simulator and assembler is generated from the ADL specification, and the feedback is used to modify the architecture. Although, ADL-driven exploration is extensively used in both academia (nML [17], ISDL [19], EXPRESSION [20], Valen-C [34], MIMOLA [45], Sim-nML [74], and LISA [96]), and industry (ARC [5], Axys [6], RADL [79], Target [87], Tensilica [88], LISATek [27], and MDES [90]), to the best of our knowledge, there has not been any effort in validating the ADL specification. It is necessary to validate the ADL specification of the architecture to ensure the correctness of both the architecture specified, as well as the generated software toolkit. Chapter 3 presents specification validation techniques for pipelined processors.

Traditionally, ADLs have been classified into two categories depending on whether they primarily capture the behavior (instruction set) or the structure of the processor. Recently, many ADLs have been proposed that capture both the structure and the behavior of the architecture.

#### 2.1.1 Behavioral ADLs

nML [17] and ISDL [19] are examples of behavior-centric ADLs. In nML, the processor's instruction-set is described as an attributed grammar with the derivations reflecting the set of legal instructions. nML has been used by the retargetable code generation environment CHESS [42] to describe DSP and ASIP (Application Specific Instruction set Processor) architectures. In ISDL, constraints on parallelism are explicitly specified through illegal operation groupings. This could be tedious for complex architectures like DSPs which permit operation parallelism (e.g. Motorola 56K) and VLIW machines with distributed register files (e.g. TI C6X). The retargetable compiler system by Yasuura et al. [34] produces code for RISC architectures starting from an instruction set processor description, and an application described in Valen-C.

Many behavioral ADLs share one common feature: a hierarchical instruction set description based on attribute grammars [36]. This feature greatly simplifies the instruction set description by exploiting the common components between operations. However, the lack of detailed pipeline and timing information prevents the use of these languages as an extensible architecture model. Information required by resourcebased scheduling algorithms cannot be obtained directly from the description. Also, it is impossible to generate cycle accurate simulators based on the behavioral descriptions without some assumptions on the architecture's control behavior, i.e., an implied architecture template has to be used.

### 2.1.2 Structural ADLs

MIMOLA [45] and UDL/I [2] are examples of ADLs that primarily capture the structure of the processor wherein the net-list of the target processor is described in a HDL (Hardware Description Language) like language. One advantage of this approach is that the same description is used for both processor synthesis and code generation. The target processor has a micro-coded architecture. Using MIMOLA, the net-list description is used to extract the instruction set [44, 45], and produce the code generator. UDL/I [2] is used for describing processors at an RT-level on a per-cycle basis. The instruction-set is automatically extracted from the UDL/I description [3], and is then used for generation of a compiler and a simulator.

In general, structural ADLs enable flexible and precise micro-architecture descriptions. The same description can be used for hardware synthesis, test generation, simulation and compilation. However, it is difficult to extract the instruction-set for retargetable compilation. The instruction set information is buried under enormous micro-architectural detail. These ADLs are more suited for hardware design than for retargetable software-toolkit generation.

#### 2.1.3 Mixed ADLs

More recently, languages that capture both the structure and the behavior of the processor, as well as detailed pipeline information have been proposed (EXPRESSION [20], RADL [79], FLEXWARE [73], MDes [90], and LISA [96]). The main characteristic of LISA is the operation-level description of the pipeline. RADL [79] is an extension of the LISA approach that focuses on explicit support of detailed pipeline behavior to enable generation of production quality cycle-accurate and phase-accurate simulators. FLEXWARE [73] and MDes [90] have a mixed-level structural/behavioral representation. FLEXWARE contains the CODESYN code-generator and the Insulin simulator for ASIPs. The simulator uses a VHDL model of a generic parameterizable machine. The application is translated from the user-defined target instruction set to the instruction set of this generic machine. The MDes [90] language used in the Trimaran system is a mixed-level ADL, intended for exploration of parameterized VLIW architectures. Information is broken down into sections (such as format, resource-usage, latency, operation, and register), based on a high-level classification of the information being represented. However, MDes allows only a restricted retargetability of

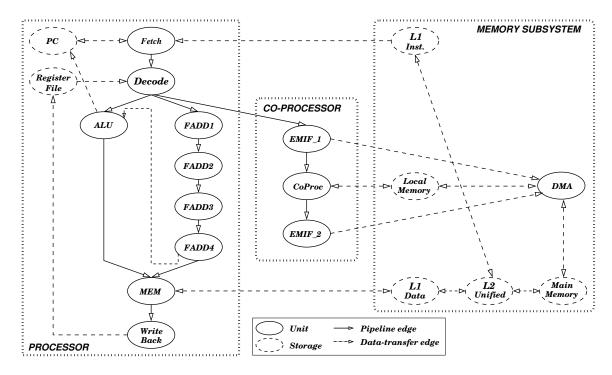

Figure 2.2: Block level description of an example architecture

the simulator to the HPL-PD processor family. MDes permits the description of the memory system, but is limited to the traditional memory architectures consisting of register files and caches. It will be difficult to describe novel memory subsystems that includes efficient memory modules (such as partitioned register files, scratch-pad SRAM, stream buffer, SDRAM, DDRAM, and RAMBUS) exhibiting a heterogeneous set of features (such as page-mode, burst-mode and pipelined accesses).

The EXPRESSION ADL also follows a mixed-level approach to facilitate DSE. Furthermore, it provides support for specification of novel memory subsystems. It avoids explicit representation of the reservation tables<sup>1</sup> by extracting them from the structural description [18]. The ADL is used to drive the generation of both compiler [21] and simulator [40].

### 2.2 Specification using EXPRESSION ADL

Our validation framework uses the EXPRESSION ADL [20] to specify processor, coprocessor, and memory architectures. The EXPRESSION ADL follows a mixedlevel approach to facilitate specification of a wide range of programmable embedded systems. We illustrate the use of the EXPRESSION ADL to describe a simple multiissue architecture consisting of a processor, a co-processor and a memory subsystem.

Figure 2.2 shows the block level description of a simple architecture. This level of detail is available in a typical architecture manual. Typically, pipeline level de-

<sup>&</sup>lt;sup>1</sup>Reservation Tables (RTs) have been used to detect conflicts between instructions that simultaneously access the same architectural resource.

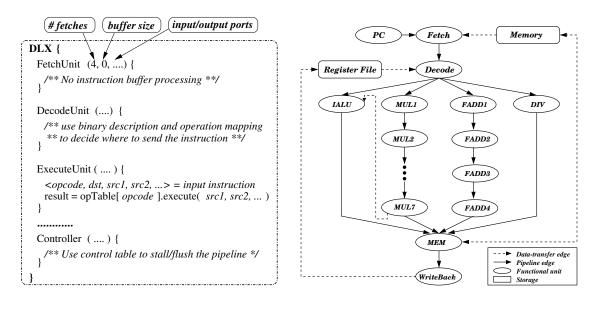

Figure 2.3: Pipeline level description of the DLX processor shown in Figure 2.2

tails are available in a micro-architecture manual. For example, Figure 2.2(a) and Figure 2.2(b) show the detailed description of the memory subsystem and the coprocessor. The memory subsystem consists of separate instruction and data memories (L1 cache), a unified L2 memory, and a main memory. The coprocessor consists of three pipeline stages: EMIF\_1, CoProc, and EMIF\_2. The coprocessor uses it local memory for computations. The data transfer between coprocessor local memory and the main memory is handled by the DMA controller shown in Figure 2.2. Similarly, Figure 2.3 shows the pipeline level description of the DLX processor shown in Figure 2.2. The DLX processor has five pipeline stages: fetch (IF), decode (ID), execute (EX), memory (MEM), and write back (WB).

The architecture shown in Figure 2.2 can issue up to two operations (an ALU or memory access operation and a coprocessor operation) per cycle. The coprocessor supports vector arithmetic operations. This section describes how to specify processor, coprocessor, and memory architectures using the EXPRESSION ADL. It also briefly describes how to capture interrupts and exceptions in the ADL.

#### 2.2.1 Processor Specification

This section describes how EXPRESSION ADL captures the structure and behavior of the DLX processor shown in Figure 2.3.

#### Structure

The structure of a processor can be viewed as a net-list with the components as nodes and the connectivity as edges. Figure 2.4(a) shows a portion of the EXPRES-SION description of the processor. It describes all the components in the structure: PC, Registers, fetch, decode, ALU, MEM, and writeback. Each component has a list of attributes. For example, the ALU unit has information regarding the number of instructions executed per cycle, timing of each instruction, supported opcodes, input/output latches, and so on.

The connectivity is established using the description of pipeline and data-transfer paths. Informally, a pipeline path is used to transfer instruction whereas a datatransfer path is used to transfer data. For example,  $\{IF \rightarrow ID \rightarrow EX \rightarrow MEM \rightarrow WB\}$  is a pipeline path, and  $\{WB \rightarrow Registers\}$  is a data-transfer path in Figure 2.3. Section 3.1.1 defines the pipeline and data-transfer paths in detail.

Figure 2.4(a) describes the five-stage pipeline as  $\{fetch, decode, execute, memory, writeback\}$ . In this particular case, the execute stage has only one component. In general, the execute stage can have multiple execution paths. Furthermore, each path can contain pipelined or multi-cycle execution units. The ADL specification also includes the description of all the data-transfer paths.

#### Behavior

The EXPRESSION ADL captures the behavior of the architecture as the description of the instruction set. The behavior is organized into operation groups, with each group containing a set of operations<sup>2</sup> having some common characteristics. For example, Figure 2.4(b) shows two operation groups. The *aluOps* includes all the operations supported by the *ALU* unit. Similarly, the *memOps* group contains all the

<sup>&</sup>lt;sup>2</sup>In this thesis we use the terms operation and instruction interchangeably.

(a) Structure

(b) Behavior

Figure 2.4: Processor specification using EXPRESSION ADL

operations supported by the MEM unit. Each instruction is then described in terms of its opcode, operands, behavior, and instruction format. Each operand is classified either as source or as destination. Furthermore, each operand is associated with a type that describes the type and size of the data it contains. The instruction format describes the fields of the instruction in both binary and assembly. Figure 2.4(b) shows the description of the *add* and *store* operations.

The ADL also captures the mapping between the structure and the behavior (and vice versa). For example, the *add* and *sub* instructions are mapped to the ALU unit, the *load* and *store* instructions are mapped to the *MEM* unit, and so on.

#### 2.2.2 Coprocessor Specification

The ADL specification of a programmable coprocessor is similar to the specification of the processor architecture described in Section 2.2.1. This section describes how the ADL captures the structure and behavior of the coprocessor shown in Figure 2.2(b). To describe the structure of the coprocessor we specify each pipeline stage of the coprocessor along with the processor pipeline as shown in Figure 2.5(a). The coprocessor pipeline has three stages. The  $EMIF_1$  (external memory interface) stage requests the DMA to transfer the data from the main memory to the coprocessor local memory. The *CoProc* stage performs the intended computation using the coprocessor local memory for accessing input operands. Results are stored back in the coprocessor memory. Finally, the  $EMIF_2$  requests the DMA to transfer the data from coprocessor memory to main memory. Figure 2.5(a) shows the description of the *CoProc* component. It supports four-cycle vector arithmetic operations.

(a) Structure

(b) Behavior

Figure 2.5: Coprocessor specification using EXPRESSION ADL

The behavior of the coprocessor is captured in terms of the operations it supports. For example, Figure 2.5(b) shows the description of a vectMul operation. Unlike normal instructions whose source and destination operands are of type register (except load/store), here source and destination operands are of type memory. The s1 and s2 fields refer to the starting addresses of two source operands for the multiplication. Similarly dst refers to the starting address of the destination operand. The length field refers to the vector length of the operation that has immediate data type.

### 2.2.3 Memory Subsystem Specification

In order to explicitly describe the memory architecture in EXPRESSION, we need to capture both structure and behavior of the memory subsystem. The memory structure refers to the organization of the memory subsystem containing memory modules and the connectivity among them. The behavior refers to the memory subsystem instruction set.

(b) Behavior

Figure 2.6: Memory subsystem specification using EXPRESSION ADL

The memory subsystem structure is represented as a netlist of memory components connected through ports and connections. The memory components are described and attributed with their characteristics (such as cache line size, replacement policy, and write policy). For example, Figure 2.6(a) shows the structure of the memory subsystem shown in Figure 2.2(a). The specification of the memory structure also includes the description of the memory pipeline and data-transfer paths. The memory subsystem instruction set represents the possible operations that can occur in the memory subsystem, such as data transfers between different memory modules or to the processor (e.g., load and store), control instructions for the different memory components (such as the DMA), or explicit cache control instructions (e.g., cache freeze, prefetch, replace and refill). For example, Figure 2.6(b) shows an internal memory data transfer operation during a load miss. The *load\_miss* operation represents data refill from L2 cache in the event of a L1 data miss.

#### 2.2.4 Specification of Interrupts and Exceptions

It is also necessary to capture exceptions and interrupts explicitly in the ADL for various reasons. First, the simulator and hardware generators require this information to accurately generate and handle exceptions. Second, the specification validation techniques use this information to analyze pipeline interactions in the presence of multiple exceptions. For example, we have used this information in Section 3.2 to verify in-order execution of pipelined processor specifications.

We classify exceptions into three categories: opcode related exceptions, exceptions related to functional units, and external exceptions. The motivation behind this classification is to enable ease of specification.

#### Opcode related exceptions

It is appropriate to describe opcode related exceptions and their actions inside the opcode specification. For example, the modified *div* operation contains the exception information as shown in Figure 2.7.

```

# Behavior: description of instruction set

......

( opcode div

(operands (s1 reg) (s2 reg) (dst reg)) (behavior dst = s1 / s2) ...

(exceptions (if (s2 == 0) throw div_by_zero) ...)

```

Figure 2.7: Specification of division\_by\_zero exception

#### **Exceptions Related to Functional Units**

Functional unit related exceptions are defined in ADL's component specification section. For example, the *Decode* unit shown in Figure 2.2 can issue upto two instructions per cycle. The first one is for the ALU pipeline and the second one is for the coprocessor pipeline. It is an exception if the second instruction is not a coprocessor

instruction. The specification of such an exception is described in the *Decode* unit as shown in Figure 2.8.

```

# Components specification

.....

( DecodeUnit Decode

(capacity 2) (timing (all 1)) (opcodes all) ...

(exceptions (if (slot2 opcode != coprocessor_type) throw illegal_slot_instruction) ...)

)

```

Figure 2.8: Specification of illegal\_slot\_instruction exception

#### **External Exceptions**

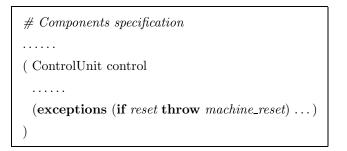

External interrupts can be specified at the processor level. We model a control unit that performs the task of a controller. The control unit is also used to perform stalling and flushing of the processor pipelines as described in Section 4.2.4. We describe external interrupts in the control unit. For example, a machine reset exception can be described in the control unit as shown in Figure 2.9. We assume that the *reset* is an external interrupt that is used to generate the internal exception *machine\_reset*.

Figure 2.9: Specification of machine\_reset exception

The mapping between exceptions and interrupts is a *many-to-one* mapping function. A class of exceptions may give rise to one interrupt, in that case the architecture implementation should ensure that only one exception from that class occurs at a time. In general, one interrupt corresponds to more than one exception. We specify the interrupts and exceptions in the control unit specification. For example, the interrupt *int1* is described in Figure 2.10. The interrupt *int1* gets generated due to any memory failure during memory operation, for example, ITLB miss or DTLB miss. It can mask several lower priority interrupts such as *int2* and *int7*.

# Components specification ControlUnit control (interrupt int1 (exceptions ITLB\_miss DTLB\_miss  $\dots$ ) (masks int2 int7...) (behavior ...) ... ) )

Figure 2.10: Specification of interrupts

We model the interrupt handler using a priority table that can accept n exception requests and generate only one interrupt per cycle. The multiple exceptions are handled in a simple and uniform manner using interrupt service register (ISR). The length of the ISR is equal to the number of interrupts possible in that architecture. One entry in the ISR corresponds to an interrupt. Control unit defines the class of exceptions that generates a particular interrupt. Each exception sets one particular bit in the ISR of the interrupt handler. Interrupt handler decides the highest priority interrupt using the interrupt masks the appropriate bits in ISR. The process of selecting highest priority interrupt continues until there are no bits set in ISR. The details on specification of exceptions and interrupts are available in [58].

### 2.3 Chapter Summary

This chapter surveyed existing ADLs in terms of their capabilities in capturing programmable architectures. Structural ADLs enable flexible and precise microarchitecture descriptions. The same description can be used for hardware synthesis, test generation, simulation and compilation. However, it is difficult to extract instruction-set information for retargetable compilation. Behavioral ADLs simplify the instruction set description by exploiting the common components between operations. However, the lack of detailed pipeline and timing information prevents the use of these languages as an extensible architecture model. Mixed ADLs capture both the structure and the behavior of the architecture.

The second part of this chapter described the use of the EXPRESSION ADL in our framework to specify programmable embedded systems. We described how to capture processor, coprocessor, and memory architectures using the ADL. Chapter 3 will present techniques to validate the ADL specification of the architecture.

## Chapter 3

## Validation of Specification

One of the most important requirements in a top-down validation methodology is to ensure that the specification (reference model) is golden. This chapter presents techniques to validate the static and dynamic behaviors of the architecture specified in an ADL. It is necessary to validate the ADL specification to ensure the correctness of both the architecture specified and the generated executable models including software toolkit and hardware implementation. The benefits of validation are two-fold. First, the process of any specification is error-prone and thus verification techniques can be used to check for correctness and consistency of the specification. Second, changes made to the processor during exploration may result in incorrect execution of the system and verification techniques can be used to ensure correctness of the modified architecture.

One of the major challenges in validating the ADL specification is to verify the pipeline behavior in the presence of hazards and multiple exceptions. There are many important properties that need to be verified to validate the pipeline behavior. For example, it is necessary to verify that each operation in the instruction set can execute correctly in the processor pipeline. It is also necessary to ensure that execution of each operation is completed in a finite amount of time. Similarly, it is important to verify the execution style (e.g., in-order execution) of the architecture. In this chapter, we verify several properties to validate the static and dynamic behaviors of the specified pipelined architecture. While these properties are by no means complete to prove

the correctness of the specification, we believe these are necessary for establishing the correctness of the specification. Additional properties can easily be added and integrated into our validation framework.

The chapter is organized as follows. Section 3.1 describes the validation techniques to ensure that the static behavior of the pipeline is well-formed by analyzing the structural aspects of the specification using a graph based model. Section 3.2 presents the techniques to verify the dynamic behavior by analyzing the instruction flow in the pipeline using a FSM based model to validate several important architectural properties such as determinism and in-order execution in the presence of hazards and multiple exceptions. Finally, Section 3.3 summarizes the chapter.

# 3.1 Validation of Static Behavior

This section presents an automatic validation framework driven by an ADL. The first step (and only manual step) in the flow is to specify the architecture using EXPRESSION ADL. A novel feature of this approach is the ability to model the pipeline structure and behavior of the processor, co-processor, and memory subsystem using a graph-based model. Based on this model, we present algorithms to ensure that the static behavior of the pipeline is well-formed by analyzing the structural aspects of the specification.

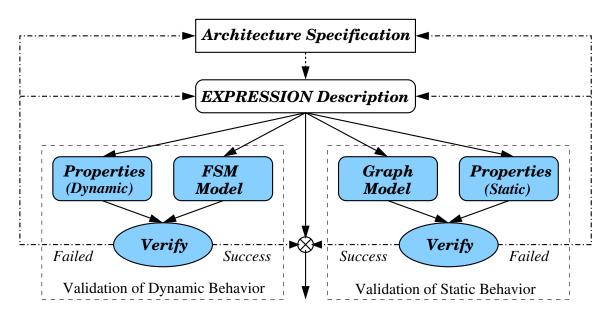

Figure 3.1 shows the flow for validating static behaviors. The designer describes the programmable architecture in an ADL. The graph model of the architecture is generated from this ADL description. Several properties are applied to ensure that the architecture is well formed.

This section describes three important steps in this methodology. First, it presents a graph-based modeling of processor, memory, and co-processor pipelines. Second, it describes several properties that must be satisfied for valid pipeline specification. Finally, it illustrates validation of pipeline specifications for several realistic architectures.

Figure 3.1: Validation of pipeline specifications

# 3.1.1 Graph-based Modeling of Pipelines

We present a graph-based modeling of architecture pipelines that captures both the structure and the behavior. The graph model presented here can be derived from a pipeline specification of the architecture described in an ADL e.g., EXPRESSION [20]. This graph model can capture processor, memory, and co-processor pipelines for a wide variety of architectures including RISC, DSP, VLIW, and superscalar architectures. In this section, we briefly describe how the graph model captures the structure and behavior of the processor using the information available in the architecture manual.

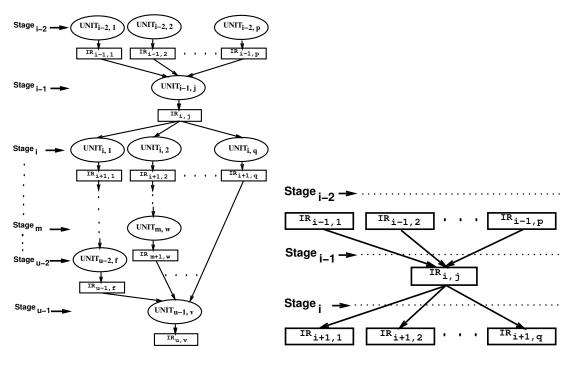

### Structure

The structure of an architecture pipeline is based on a block diagram view available in the processor manual, and is modeled as a graph  $G_S = (V_S, E_S)$ , where  $V_S$  denotes a set of components and  $E_S$  consists of a set of edges.  $V_S$  consists of two types of components:  $V_{unit}$  and  $V_{storage}$ .  $V_{unit}$  is a set of functional units (e.g., ALU), and  $V_{storage}$  is a set of storages (e.g., register files).  $E_S$  consists of two types of edges.

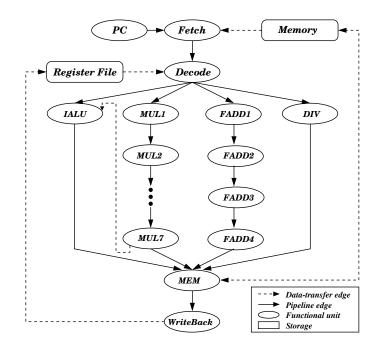

Figure 3.2: An example architecture

$E_{data\_transfer}$  is a set of data-transfer edges, and  $E_{pipeline}$  is a set of pipeline edges. An edge (pipeline or data-transfer) indicates connectivity between two components. A data-transfer edge transfers data between units and storages. A pipeline edge transfers instruction (operation) between two units.

$$V_{S} = V_{unit} \cup V_{storage}$$

$$E_{S} = E_{data\_transfer} \cup E_{pipeline}$$

$$E_{data\_transfer} \subseteq \{V_{unit}, V_{storage}\} \times \{V_{unit}, V_{storage}\}$$

$$E_{pipeline} \subseteq V_{unit} \times V_{unit}$$

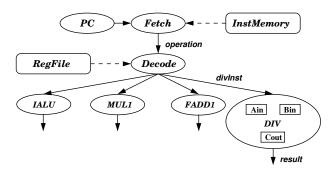

For illustration, we use a simple multi-issue architecture consisting of a processor, a co-processor and a memory subsystem. Figure 3.2 shows the graph-based model of this architecture that can issue up to three operations (an ALU operation, a floatingpoint addition operation, and a coprocessor operation) per cycle. Figure 3.2 is obtained from Figure 2.2. We have added a four-stage floating point adder (FADD) and a feedback path from the FADD pipeline to the ALU pipeline. In the figure, oval boxes denote units, dotted ovals are storages, bold edges are pipeline edges, and dotted edges are data-transfer edges. A path from a root node (e.g., Fetch) to a leaf node (e.g, WriteBack) consisting of units and pipeline edges is called a *pipeline path*. For example, one of the pipeline paths is {*Fetch, Decode, ALU, MEM, Write-Back*}. A path from a unit to main memory or register file consisting of storages and data-transfer edges is called a *data-transfer path*. For example, {*MEM, L1, L2, MainMemory*} is a data-transfer path.

### Behavior

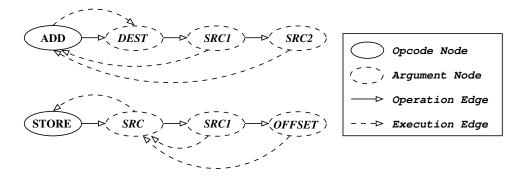

The behavior of the architecture is typically captured by the instruction-set (ISA) description in the processor manual. It consists of a set of operations that can be executed on the architecture. Each operation in turn consists of a set of fields (e.g. opcode, arguments) that specify, at an abstract level, the execution semantics of the operation. We model the behavior as a graph  $G_B = (V_B, E_B)$ , where  $V_B$  is a set of nodes, and  $E_B$  is a set of edges. The nodes represent the fields of each operation, while the edges represent orderings between the fields. The behavior graph  $G_B$  is a set of disjointed sub-graphs, and each sub-graph is called an *operation graph* (or simply an operation). Figure 3.3 shows a portion of the behavior (consisting of two operation graphs) for the example processor shown in Figure 3.2.

$$V_B = V_{opcode} \cup V_{argument}$$

$$E_B = E_{operation} \cup E_{execution}$$

$$E_{operation} \subseteq V_{opcode} \times V_{argument} \cup V_{argument} \times V_{argument}$$

$$E_{execution} \subseteq V_{argument} \times V_{argument} \cup V_{argument} \times V_{opcode}$$

Nodes are of two types.  $V_{opcode}$  is a set of opcode nodes that represent the opcode (i.e. mnemonic), and  $V_{argument}$  is a set of argument nodes that represent argument fields (i.e., source and destination arguments). In Figure 3.3, the ADD and STORE nodes are opcode nodes, while the others are argument nodes. Edges are also of two types.  $E_{operation}$  is a set of operation edges that link the fields of the operation and also specify the syntactical ordering between them. On the other hand,  $E_{execution}$  is

Figure 3.3: A fragment of the behavior graph

a set of execution edges that specify the execution ordering between the fields. In Figure 3.3, the solid edges represent operation edges while the dotted edges represent execution edges. For the ADD operation, the operation edges specify that the syntactical ordering is opcode followed by DEST, SRC1 and SRC2 arguments (in that order), and the execution edges specify that the SRC1 and SRC2 arguments are executed (i.e., read) before the ADD operation is performed. Finally, the DEST argument is written.

### Mapping between Structure and Behavior

The mapping between the structure and the behavior is captured explicitly in the ADL. This information is available in the architecture manual as mapping between the instruction set and the functional units. It other words, the manual describes what operations are supported by which functional units in the architecture. We define a set of mapping functions that map nodes in the structure to nodes in the behavior (and vice-versa). The *unit-to-opcode (opcode-to-unit)* mapping is a bi-directional function that maps unit nodes in the structure to opcode nodes in the behavior. The *unit-to-opcode* mappings for the architecture in Figure 3.2 include mappings from *Fetch* unit to opcode  $\{ADD, FADD\}$ , ALU unit to opcode ADD, FADD1 unit to opcode FADD etc. The *argument-to-storage (storage-to-argument)* mapping is a bi-directional function that maps argument nodes in the behavior to storage nodes in the structure. For example, the *argument-storage* mappings for the ADD operation are mappings from  $\{DEST, SRC1, SRC2\}$  to *RegisterFile*.

Each functional unit (with read or write ports) supports certain data-transfer operations. These operations can be derived from the above mapping functions. For example, the *Decode* unit of Figure 3.2 supports register read (regRead) for ADD and LD opcodes; the *MEM* unit supports data read (dataRead) and data write (dataWrite) from L1 data cache; the *Fetch* unit supports instruction read (instRead) from L1 instruction cache; the *WriteBack* unit supports register write (regWrite). Similarly, each storage supports certain data-transfer operations. For example, the *RegisterFile* of Figure 3.2 supports regRead and regWrite; L1 data cache supports dataRead and dataWrite, and so on.

## **3.1.2** Validation of Pipeline Specifications

Based on the graph model presented in the previous section, the ADL specification of architecture pipelines can be validated. In this section, we describe some of the properties used in our framework for validating pipelined architecture specifications.

### **Connectedness Property**

The connectedness property ensures that each component is connected to other component(s). As pipeline and data-transfer paths are connected regions of the architecture, this property holds if each component belongs to at least one pipeline or data-transfer path.

$$\forall v_{comp} \in V_S, (\exists G_{PP} \in \mathbf{G_{PP}}, s.t. v_{comp} \in G_{PP}) \lor (\exists G_{DP} \in \mathbf{G_{DP}}, s.t. v_{comp} \in G_{DP})$$

where  $\mathbf{G}_{\mathbf{PP}}$  is a set of pipeline paths and  $\mathbf{G}_{\mathbf{DP}}$  is a set of data-transfer paths.

Algorithm 1 presents the pseudo-code for verifying the connectedness property. The algorithm requires the graph model G of the architecture as input. It also requires all the component lists as input. The first step is to unmark the entries in all the input lists. Each input list contains all the respective components in the graph. For example, the *ListOfUnits* contains all the units in the graph G. Next, the graph is traversed in breadth-first manner and the visited components are marked. For example, when a unit u is visited during traversal, it is marked in *ListOfUnits*.

Finally, the algorithm returns true if all the entries are marked in all the input lists. It returns false if there are any unmarked entries in any of the input lists, and it reports them.

| Algorithm 1: Verify Connectedness                                                                |

|--------------------------------------------------------------------------------------------------|

| <b>Inputs</b> : i. Graph model of the architecture $G$                                           |

| ii. $ListOfUnits$ : list of units in the graph G                                                 |

| iii. $ListOfStorages:$ list of storages in the graph G                                           |

| <b>Outputs</b> : i. <i>True</i> , if the graph model satisfies this property else <i>false</i> . |

| ii. In case of failure, report the disconnected components.                                      |

| Begin                                                                                            |

| Unmark all the entries in all the input lists.                                                   |

| InsertQ(root, $Q$ ) /* Put root node of $G$ in queue $Q$ */                                      |

| while $Q$ is not empty                                                                           |

| Node $n = \text{DeleteQ}(Q)$ /* Remove the front element of $Q^*$ /                              |

| Mark $n$ as visited in $G$                                                                       |

| <b>case</b> type of node $n$                                                                     |

| unit: Mark $n$ in $ListOfUnits$                                                                  |

| storage: Mark $n$ in $ListOfStorages$                                                            |

| endcase                                                                                          |

| for each successor node $s$ of $n$                                                               |

| <b>if</b> s is not visited InsertQ(s, $Q$ )                                                      |

| $\mathbf{end}\mathbf{for}$                                                                       |

| endwhile                                                                                         |

| Return <i>true</i> if all the entries are marked in all of the input lists;                      |

| false otherwise, and report the unmarked components.                                             |

| End                                                                                              |

Each node of the graph is visited only once. The time and space complexity of the algorithm is O(n), where n is the number of nodes in the graph G. Each node of the graph can be either unit or storage.

# False Pipeline and Data-transfer Paths

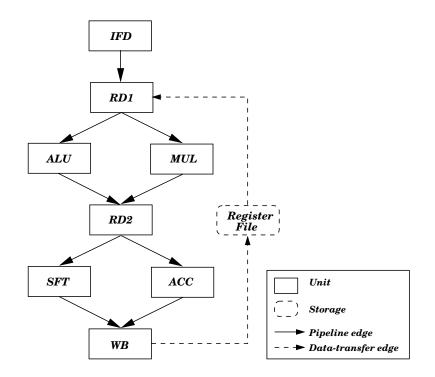

According to the definition of pipeline paths, there may exist pipeline paths that are never activated by any operation. Such pipeline paths are said to be *false*. For example, let us use another architecture shown in Figure 3.4 that executes two operations: ALU-shift (alus) and multiply-accumulate (mac). This processor has unit-toopcode mappings between ALU unit and opcode alus, between SFT and alus, between MUL and mac, and between ACC and mac. Also, there are unit-to-opcode mappings between each of {*IFD*, *RD1*, *RD2*, *WB*} and alus, and each of {*IFD*, *RD1*, *RD2*, *WB*} and mac. This processor has four pipeline paths: {*IFD*, *RD1*, *ALU*, *RD2*, *SFT*, *WB*}, {*IFD*, *RD1*, *MUL*, *RD2*, *ACC*, *WB*}, {*IFD*, *RD1*, *ALU*, *RD2*, *ACC*, *WB*}, and {*IFD*, *RD1*, *MUL*, *RD2*, *SFT*, *WB*}. However, the last two pipeline paths cannot be activated by any operation. Therefore, they are false pipeline paths. Since these false pipeline paths may become false paths depending on the detailed structure of RD2, they should be detected at a higher level of abstraction to ease the later design phases.

From the view point of SOC architecture exploration, we can view the false pipeline paths as an indication of potential behaviors that are not explicitly defined in the ADL description. These false pipeline paths can be used to perform valid computations. This opens up avenues for further exploration experiments for cost, power, and performance by adding new instructions to activate the false pipeline paths.

Formally, a pipeline path  $G_{PP}(V_{PP}, E_{PP})$  is false if the intersection of opcodes supported by the units in the pipeline path is empty.

$$\bigcap_{v_{unit} \in V_{PP}} f_{unit-opcode}(v_{unit}) = \phi \tag{3.1}$$

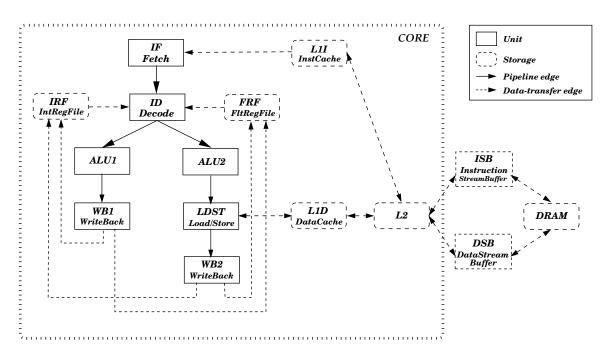

Similarly, there may exist data-transfer paths in the specification that are never activated by any operation. Such data-transfer paths are said to be *false*. For example, let us use another architecture shown in Figure 3.5 that has seven possible data-transfer operations: integer-register-read (IregRd), float-register-read (FregRd), integer-register-write (IregWr), float-register-write (FregWr), load-data-frommemory (ldData), load-instruction-from-memory (ldInst), and store-data-in-memory (stData). The *Decode (ID)* unit has mappings for *IregRd* and *FregRd*. There are mappings between each of {*WB1*, *WB2*} and {*IregWr*, *FregWr*}, each of {*IF*, *L1I*, *ISB*} and *ldInst*, each of {*LDST*, *L1D*, *DSB*} and {*ldData*, *stData*}, and each of {*L2*, *DRAM*} and {*ldData*, *stData*, *ldInst*}. This processor has ten data-transfer

Figure 3.4: An example processor with false pipeline paths

paths:  $\{IRF, ID\}$ ,  $\{FRF, ID\}$ ,  $\{WB1, IRF\}$ ,  $\{WB1, FRF\}$ ,  $\{WB2, IRF\}$ ,  $\{WB2, IRF\}$ ,  $\{WB2, FRF\}$ ,  $\{IF, L1I, L2, ISB, DRAM\}$ ,  $\{LDST, L1D, L2, DSB, DRAM\}$ ,  $\{IF, L1I, L2, DSB, DRAM\}$ ,  $\{LDST, L1D, L2, ISB, DRAM\}$ . However, the last two data-transfer paths cannot be activated by any operation. Therefore, they are false data-transfer paths. If ALU1 supports only floating-point operations, the fourth path ( $\{WB1, IRF\}$ ) becomes a false data-transfer path.

Formally, a data-transfer path  $G_{DP}(V_{DP}, E_{DP})$  is false if the intersection of datatransfer operations supported by the units and storages  $(f_{node-operation})$  in the datatransfer path is empty.

$$\bigcap_{v_{node} \in V_{DP}} f_{node-operation}(v_{node}) = \phi$$

(3.2)

Algorithm 2 presents the pseudo-code for verifying false pipeline and data-transfer paths. The algorithm requires the graph model G as input. It traverses the graph in depth-first manner along each pipeline and data-transfer path. Each unit u has a list of supported opcodes  $SuppOpList_u$ . Each node n (unit or storage) also maintains

```

Algorithm 2: Verify False Pipeline and Data-transfer Paths

Input: Graph model of the architecture G.

Outputs: i. True, if the graph model satisfies this property else false.

ii. In case of failure, report the list of false pipeline and data-transfer paths.

Begin

Push (root, S); FalsePPpathList = \{\}; FalseDPpathList = \{\};

while S is not empty

Node n = \text{Pop}(S); Mark n as visited.

case node type of n

unit: if n is the root node

OutOpList_n = SuppOpList_n // Send supported opcodes to children

else /* p is the recently visited parent */

InOpList_n = OutOpList_p; OutOpList_n = SuppOpList_n \cap InOpList_n

if n has read or write ports

OutDTopList_n = ComputeDataTransferOps(OutOpList_n)

if OutDTopList_n is empty

for all the data-transfer paths fDP from n to any leaf nodes

Insert fDP in FalseDPpathList.

else for each children storage node st of n, Push(st, S)

if OutOpList_n is empty

Get path pp from n by tracing recently visited parents till root

for all pipeline paths ppEnd from n to any leaf nodes

Append ppEnd to pp to get fPP; Insert fPP in FalsePPpathList.

else for each children unit u of n, Push(u, S)

storage: InDTopList_n = OutDTopList_p

OutDTopList_n = SuppDTopList_n \cap InDTopList_n

if OutDTopList_n is empty

Get path dp from n by tracing recently visited parents till any unit

for all data-transfer paths dpEnd from n to any leaf nodes

Append dpEnd to dp to generate false data-transfer path fDP.

Insert fDP in FalseDPpathList.

endfor

else for each children storage node st of n, Push(st, S)

endcase

endwhile

if FalsePPpathList and FalseDPpathList are empty return true;

else return false and report FalsePPpathList and FalseDPpathList.

End

```

four temporary lists:  $OutOpList_n$ ,  $OutDTopList_n$ ,  $InOpList_n$ , and  $InDTopList_n$ . The  $OutOpList_n$  is the list of opcodes produced by unit n and sent to its children units. The  $OutDTopList_n$  is the list of data-transfer operations produced by node (unit or storage) n and sent to its children storages. The  $InOpList_n$  is the list that is used by unit n to copy the  $OutOpList_p$ , the output list of the recently visited parent p. Similarly, the  $InDTopList_n$  is the list that is used by storage n to copy the  $OutDTopList_p$ , the output list of the recently visited parent p. Each unit n performs intersection of  $InOpList_n$  and  $SuppOpList_n$  and send the result  $OutOpList_n$  to its children units. If  $OutOpList_n$  is empty, all the pipeline paths that use the path from n to root (via recently visited parents) are false pipeline paths. A unit with read or write ports computes data transfer operations using the method described in Section 3.1.1. A storage computes  $OutDTopList_n$  by performing intersection of  $SuppDTopList_n$  and the input list  $InDTopList_n$ . If  $OutDTopList_n$  is empty, all the data-transfer paths that use the path from storage n to any unit via recently visited parents are false data-transfer paths. The algorithm returns true if there are no false pipeline or data-transfer paths. It returns false if there are any false pipeline or data-transfer paths, and reports them.

If there are *n* nodes, *x* pipeline and data-transfer paths in the graph and the number of opcodes supported by the processor is *p*, the time complexity of the algorithm is  $O(x \times n \times (x + plogp))$  and space complexity is  $O(n \times p)$ . The supported opcode list in each node is a sorted list.

### **Completeness Property**

The completeness property confirms that all operations must be executable. An operation *op* is executable if there exists a pipeline path  $G_{PP}(V_{PP}, E_{PP})$  on which *op* is executable. An operation *op* is executable on a pipeline path  $G_{PP}(V_{PP}, E_{PP})$  if both Condition 3.1 and 3.2 hold.

**Condition 3.1:** All units in  $V_{PP}$  support the operation *op*. More formally, the following condition holds where  $v_{opcode}$  is the opcode of the operation *op*.

$$\forall v_{unit} \in V_{PP}, v_{opcode} \in f_{unit-opcode}(v_{unit}).$$

(3.3)

Figure 3.5: An example processor with false data-transfer paths