# SYSTEM-ON-CHIP VULNERABILITY ANALYSIS AND MITIGATION TECHNIQUES

By YUANWEN HUANG

## A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# UNIVERSITY OF FLORIDA

© 2017 Yuanwen Huang

To my family

#### ACKNOWLEDGMENTS

Firstly, I would like to express my sincere gratitude to my advisor Prof. Prabhat Mishra for the continuous support of my Ph.D. study, for his patience, motivation and immense knowledge. His guidance helped me in all the time of research and writing this dissertation. He is the person who made this dissertation come true.

Besides my advisor, I would like to thank the rest of my dissertation committee: Prof. Sartaj Sahni, Prof. Shigang Chen, Prof. Sanjay Ranka, and Prof. Ann Gordon-Ross for their insightful comments and encouragement, but also for the hard questions which incented me to view my research from various perspectives. I also appreciate the help from Prof. Swarup Bhunia and Prof. Anupam Chattopadhyay.

I thank my fellow labmates: Farimah Farahmandi, Terek Arce, Yangdi Lyu, Subodha Charles, Alif Ahmed, Anirudh Canumalla, Emre Ozgener, and Jonathan Cruz. It was my great pleasure to work with you. The friendship with you has made my Ph.D. life so delightful, especially when I was stressed with experiments and deadlines.

Last but not least, I sincerely thank my parents and my sister for their love, support and encouragement. They gave me the courage to take my own path, the strength to go through the difficult times, and the perseverance to try again and again until I find the way. This dissertation would not be possible without their unconditional love. I dedicate this dissertation to them.

This work was partially supported by grants from National Science Foundation (CCF-1218629, CNS-1526687 and CNS-1441667), Semiconductor Research Corporation (2014-TS-2554) and Cisco Systems (F020375). Any opinions, findings, conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the funding agencies.

4

# TABLE OF CONTENTS

|      |                   |                                                                                                                                                                                | page                                                 |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| ACK  | NOV               | VLEDGMENTS                                                                                                                                                                     | 4                                                    |

| LIST | OF                | TABLES                                                                                                                                                                         | 8                                                    |

| LIST | OF                | FIGURES                                                                                                                                                                        | 9                                                    |

| ABS  | TRA               | CT                                                                                                                                                                             | 12                                                   |

| CHA  | PTE               | R                                                                                                                                                                              |                                                      |

| 1    | INT               | RODUCTION                                                                                                                                                                      | 13                                                   |

|      | 1.1<br>1.2<br>1.3 | Vulnerabilities in System-on-Chip                                                                                                                                              | 15<br>16<br>16<br>17<br>19<br>22                     |

| 2    | BAC               | CKGROUND AND RELATED WORK                                                                                                                                                      | 25                                                   |

|      | 2.1               | Dynamic Cache Reconfiguration for Vulnerability Reduction2.1.1Cache Vulnerability2.1.2Dynamic Cache Reconfiguration2.1.3Partially Protected Caches for Vulnerability Reduction | 25<br>25<br>28<br>31                                 |

|      | 2.2               | Trace Buffer Attack on AES                                                                                                                                                     | 33<br>34<br>35                                       |

|      | 2.3               | Hardware Trojan Attacks and Detection Techniques2.3.1Hardware Trojan Attacks2.3.2Trojan Detection Approaches                                                                   | 36<br>36<br>37                                       |

| 3    | VUL               | NERABILITY AND ENERGY-AWARE CACHE RECONFIGURATION .                                                                                                                            | 41                                                   |

|      | 3.1<br>3.2        | Motivation: Illustrative Example                                                                                                                                               | $     42 \\     44 \\     44 \\     45 \\     46   $ |

|      | 3.3               | Intra-task Cache Reconfiguration                                                                                                                                               | $50 \\ 52 \\ 54 \\ 56$                               |

|      | 3.4               | Experiments                                                                                                                                                                    | $\frac{59}{59}$                                      |

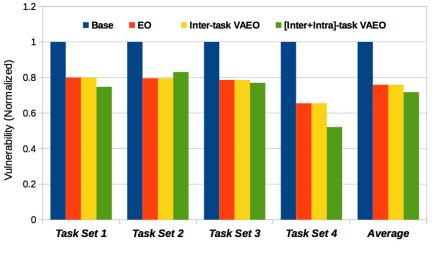

|   |     | 3.4.2<br>3.4.3 | VAEO and Intra-task VAEO Configurations               | . 63  |

|---|-----|----------------|-------------------------------------------------------|-------|

|   | 3.5 | 3.4.4          | Hardware Overhead                                     |       |

|   | 5.0 | Summ           | nary                                                  | . 07  |

| 4 |     |                | ABILITY-AWARE RECONFIGURATION FOR PARTIALLYCED CACHES | . 68  |

|   | 4.1 | Energ          | y Models                                              | . 69  |

|   |     | 4.1.1          | Energy Model for Unprotected Cache                    |       |

|   |     | 4.1.2          | Energy Model for Protected Cache                      |       |

|   | 4.2 | Cache          | e Reconfiguration of PPC                              |       |

|   |     | 4.2.1          | Data Partitioning                                     |       |

|   |     | 4.2.2          | Cache Exploration                                     |       |

|   |     | 4.2.3          | Fast Exploration                                      |       |

|   |     |                | 4.2.3.1 Fast exploration of caches (FEC)              |       |

|   | 4.0 | Ð              | 4.2.3.2 Fast exploration of caches and data (FECD)    |       |

|   | 4.3 | -              | iments                                                |       |

|   |     | 4.3.1          | Synergistic Exploration                               |       |

|   |     | 4.3.2          | Comparison with Previous Works                        |       |

|   |     |                | 4.3.2.1Improvement to DCR4.3.2.2Improvement to PPC    |       |

|   |     | 4.3.3          | Fast Exploration                                      |       |

|   | 4.4 |                | hary                                                  |       |

|   |     |                |                                                       |       |

| 5 | VUI | LNERA          | BILITY-AWARE CACHE TUNING FOR MULTICORE SYSTEMS       | 91    |

|   | 5.1 | Mode           | ling Systems with Reconfigurable Caches               | . 92  |

|   |     | 5.1.1          | Multicore Architecture Model                          | . 92  |

|   |     | 5.1.2          | Energy and Vulnerability Models                       | . 93  |

|   |     | 5.1.3          | Illustrative Example                                  | . 94  |

|   |     | 5.1.4          | Problem Formulation                                   |       |

|   | 5.2 | Vulne          | rability-Aware DCR+CP                                 | . 97  |

|   |     | 5.2.1          | Task Profiling                                        |       |

|   |     | 5.2.2          | Optimization on Each Core                             |       |

|   |     | 5.2.3          | Optimization Across All Cores                         |       |

|   | 5.3 | Exper          | ments                                                 |       |

|   |     | 5.3.1          | Deadline and Vulnerability Threshold                  |       |

|   |     | 5.3.2          | Vulnerability-Aware Energy Reduction                  |       |

|   | 5.4 | Summ           | nary                                                  | . 106 |

| 6 | TRA | ACE BI         | UFFER ATTACK ON AES CIPHER                            | . 109 |

|   | 6.1 | Trace          | Buffer Attack with RTL Knowledge                      | . 110 |

|   |     | 6.1.1          | Attack Model                                          | . 110 |

|   |     | 6.1.2          | Determine Trace Buffer Signals                        | . 111 |

|   |     | 6.1.3          | Signal Restoration                                    | . 113 |

|     | 6.2                                       | Trace Buffer Attack without RTL Knowledge6.2.1Mapping Signals to Algorithm Variables6.2.2Attack by Taking Advantage of Rijndael's Key Expansion                                                                                                                                                                                                                                                                                 | 114<br>114<br>117                                                  |

|-----|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|     | 6.3                                       | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                            | 122<br>124                                                         |

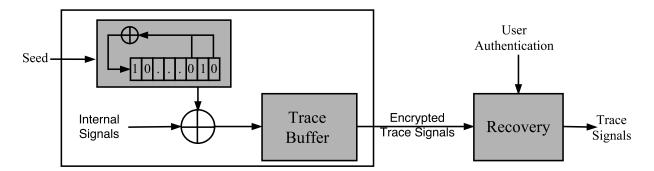

|     | $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Proposed Countermeasures                                                                                                                                                                                                                                                                                                                                                                                                        | 128<br>130<br>133                                                  |

| 7   | STA                                       | TISTICAL TEST GENERATION FOR TROJAN DETECTION                                                                                                                                                                                                                                                                                                                                                                                   | 134                                                                |

|     | <ul><li>7.1</li><li>7.2</li></ul>         | MERS: Increasing the Trojan Detection Sensitivity7.1.1Multiple Excitation of Rare Switching7.1.2Hamming Distance Based Reordering7.1.3Simulation Based ReorderingExperiments7.2.1Experimental Setup                                                                                                                                                                                                                             | 136<br>138<br>140<br>141<br>143<br>143                             |

|     | 7.3                                       | <ul> <li>7.2.2 Evaluation Criteria</li> <li>7.2.3 Exploration of N</li> <li>7.2.4 Side-effect of MERS: Increased TotalSwitch</li> <li>7.2.5 Reordering and Exploration of C</li> <li>7.2.6 Effectiveness of MERS in Creating Trojan Activity</li> <li>7.2.7 Side Channel Sensitivity Improvement</li> <li>7.2.8 Calibration and Multiple-Parameter Side-Channel Analysis</li> <li>7.2.9 Scalability to Large Designs</li> </ul> | 143<br>144<br>146<br>146<br>147<br>150<br>151<br>152<br>153<br>154 |

| 8   | CON                                       | ICLUSIONS AND FUTURE WORK                                                                                                                                                                                                                                                                                                                                                                                                       | 155                                                                |

|     | 8.1<br>8.2                                |                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{c} 155\\ 157 \end{array}$                           |

| APP | END                                       | IX: LIST OF PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                        | 159                                                                |

| REF | ERE                                       | NCES                                                                                                                                                                                                                                                                                                                                                                                                                            | 161                                                                |

| BIO | GRA                                       | PHICAL SKETCH                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                                                |

# LIST OF TABLES

| Tabl |                                                                                                                                                                                   | page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3-1  | Four task sets with twelve benchmarks                                                                                                                                             | 61   |

| 3-2  | Overhead of profile table (180nm technology)                                                                                                                                      | 66   |

| 3-3  | Overhead of profile table (65nm technology)                                                                                                                                       | 66   |

| 4-1  | Vulnerability reduction compared to [5]                                                                                                                                           | 82   |

| 4-2  | DCR+PPC(VulMin): vulnerability minimization under energy constraints                                                                                                              | 87   |

| 4-3  | DCR+PPC(EnergyMin): energy minimization under vulnerability constraints .                                                                                                         | 87   |

| 4-4  | Simulation time for three exploration strategies: $\mathit{Exhaustive}, \mathit{FEC}$ and $\mathit{FECD}$ .                                                                       | 87   |

| 5-1  | Task sets from MiBench [46] and CPU2000 [57] benchmarks $\ldots$ .                                                                                                                | 108  |

| 5-2  | TASK SET 1: CACHE CONFIG $([c_1, c_D, w_k])$                                                                                                                                      | 108  |

| 5-3  | TASK SET 9: CACHE CONFIG $([c_1, c_D, w_k])$                                                                                                                                      | 108  |

| 6-1  | Recover when the fourth word of the round key register are known                                                                                                                  | 120  |

| 6-2  | Restore the primary key from the available trace buffer content                                                                                                                   | 125  |

| 6-3  | Signal restoration for iterative AES-128                                                                                                                                          | 127  |

| 6-4  | Pipelined AES-128, AES-192 and AES-256.                                                                                                                                           | 130  |

| 6-5  | Comparison of LFSR-based and PUF-based countermeasures                                                                                                                            | 133  |

| 7-1  | Runtime for MERS test generation and test reordering                                                                                                                              | 144  |

| 7-2  | Comparison of MERS (N=1000) with Random (10K) for average<br>MaxDeltaSwitch and average AvgDeltaSwitch                                                                            | 150  |

| 7-3  | Comparison of MERS (N=1000) with Random (10K) for average $MaxRelativeSwitch$ (Side Channel Sensitivity) and average $AvgRelativeSwitch$ .                                        | 151  |

| 7-4  | Comparison of average <i>Side Channel Sensitivity</i> between Random (10K),<br>MERO, and MERS testsets, N=1000, C=5 for MERS-s, over 1000 random<br>samples of 4-trigger Trojans. | 152  |

| 7-5  | Comparison of average <i>Side Channel Sensitivity</i> between Random (10K),<br>MERO, and MERS testsets, N=1000, C=5 for MERS-s, over 1000 random<br>samples of 8-trigger Trojans. | 152  |

# LIST OF FIGURES

| Figu | <u>`igure</u>                                                                                                                                                                                                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-1  | The Internet of Things (IoT) is pervasive in every aspect of our daily life                                                                                                                                           | 13 |

| 1-2  | IoT devices typically contain a System-on-Chip (SoC) computing platform with reusable hardware IP components.                                                                                                         | 14 |

| 1-3  | System-on-Chip vulnerabilities.                                                                                                                                                                                       | 15 |

| 1-4  | Overview of trace buffer in system validation and debug                                                                                                                                                               | 18 |

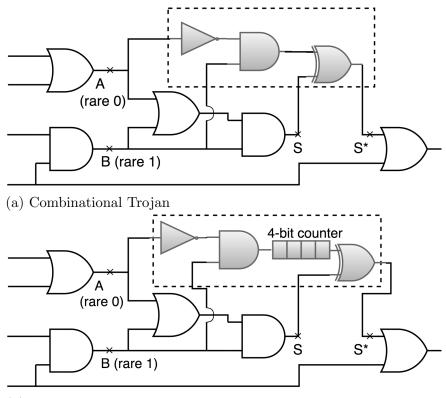

| 1-5  | Example of a combinational and a sequential Trojan with triggers from two rare internal nodes A and B                                                                                                                 | 21 |

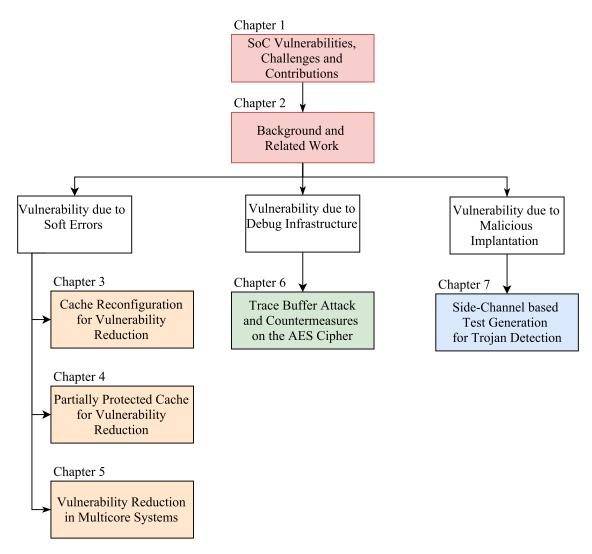

| 1-6  | Dissertation Outline                                                                                                                                                                                                  | 24 |

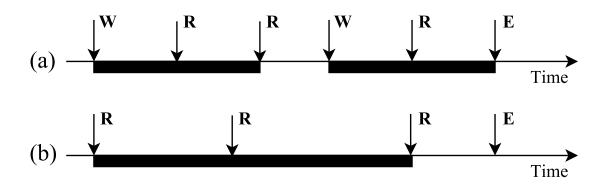

| 2-1  | Vulnerable intervals of two data elements in cache (where W=Write Access, R=Read Access, E=Evict). (a) data with both <i>write</i> and <i>read</i> accesses; (b) data with only <i>read</i> accesses.                 | 27 |

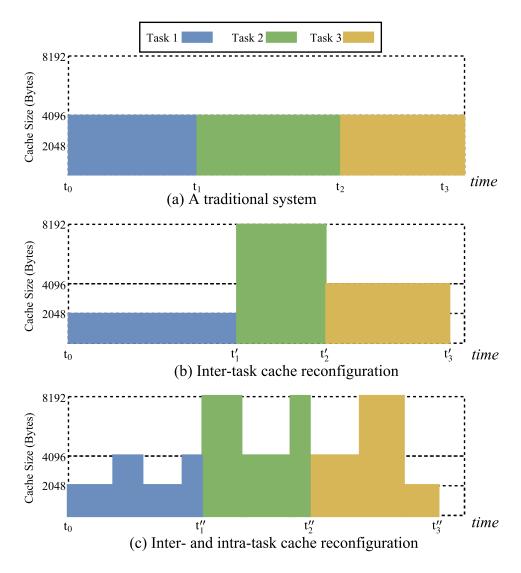

| 2-2  | DCR in a system with three tasks.                                                                                                                                                                                     | 30 |

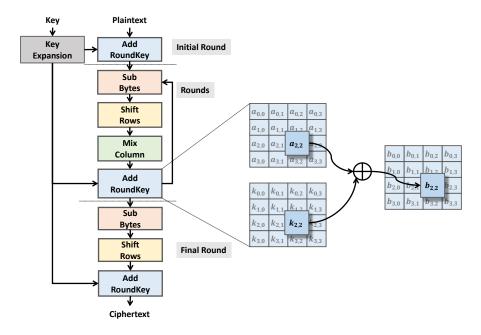

| 2-3  | AES Encryption Flow                                                                                                                                                                                                   | 34 |

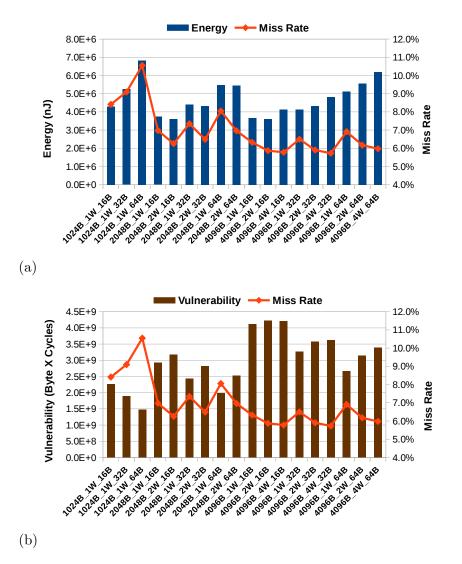

| 3-1  | Energy and vulnerability values of <i>pegwit</i> benchmark using different cache configurations. (a) Energy and miss rate, (b) Vulnerability and miss rate                                                            | 42 |

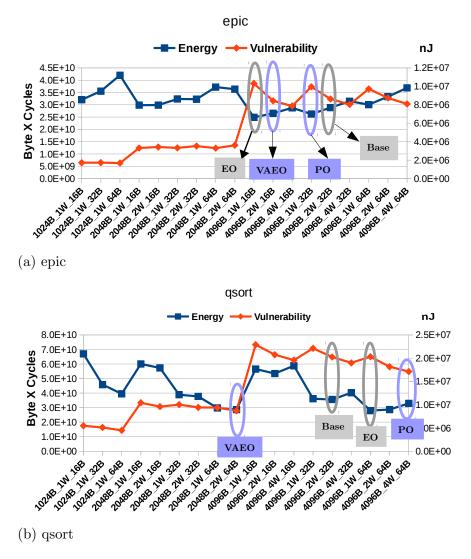

| 3-2  | VAEO and PO configurations of two benchmarks: (a) <i>epic</i> and (b) <i>qsort</i>                                                                                                                                    | 48 |

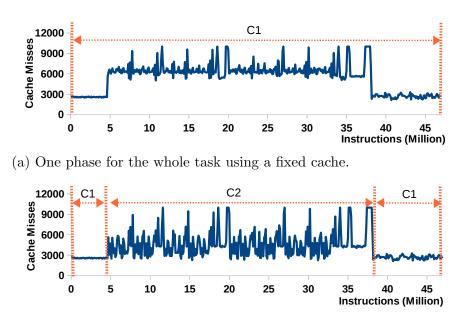

| 3-3  | Data cache misses for benchmark <i>qsort</i> . (a) Without intra-task reconfiguration, using one cache for the whole task; (b) With intra-task reconfiguration, using a different cache for each of the three phases. | 51 |

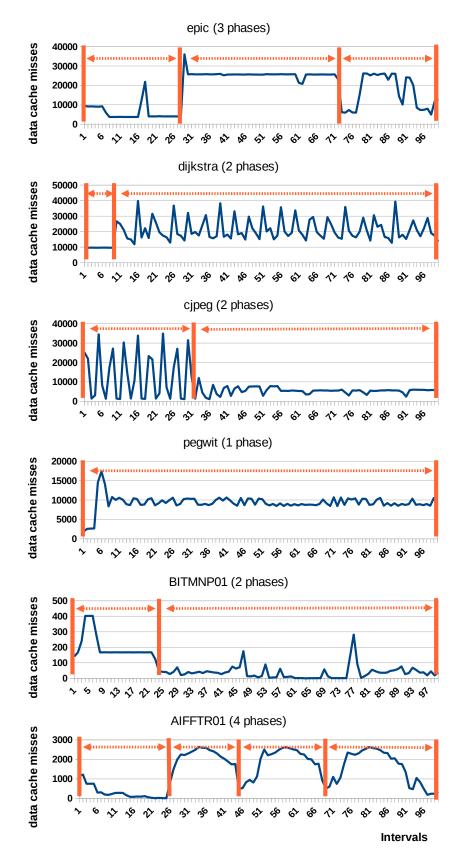

| 3-4  | Phases identified for different benchmarks.                                                                                                                                                                           | 53 |

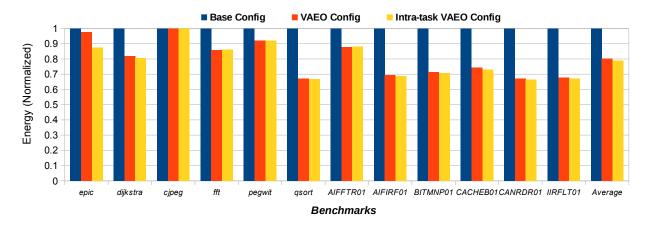

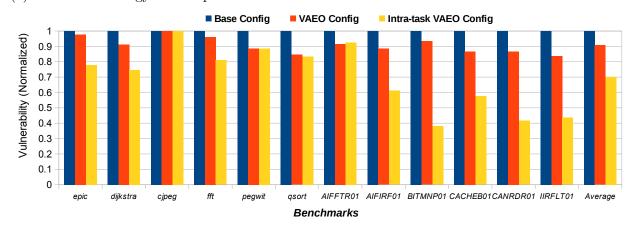

| 3-5  | Comparison of DL1 energy consumption and vulnerability of single tasks for<br>Base, VAEO and Intra-task VAEO configurations. (a) Data cache energy<br>consumption, (b) Data cache vulnerability.                      | 59 |

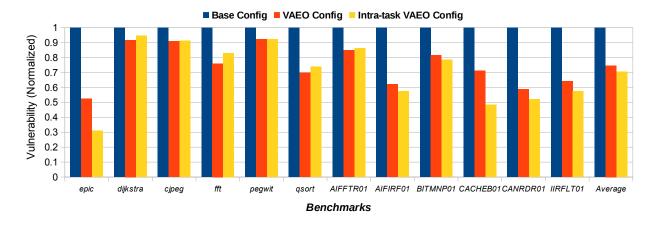

| 3-6  | Comparison of IL1 energy consumption and vulnerability of single tasks for<br>Base, VAEO and Intra-task VAEO configurations. (a) Instruction cache energy<br>consumption, (b) Instruction cache vulnerability.        | 60 |

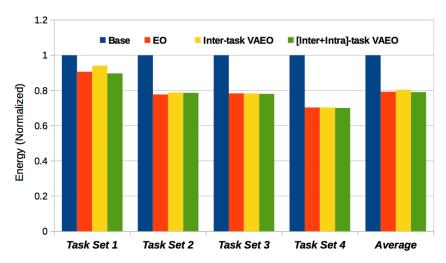

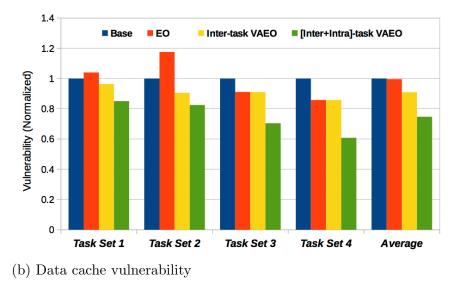

| 3-7  | (a) Data cache energy and (b) Data cache vulnerability.                                                                                                                                                               | 63 |

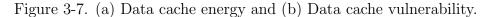

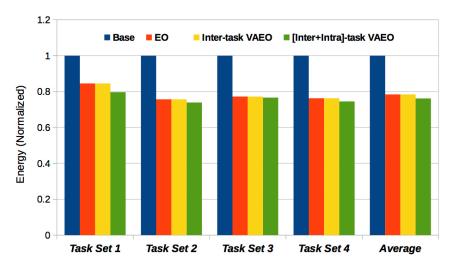

| 3-8  | (a) Instruction cache energy and (b) Instruction cache vulnerability.                                                                                                                                                 | 64 |

| 4-1  | A reconfigurable PPC-base architecture with one protected cache and the other<br>unprotected cache at the same level of hierarchy.                                                                                    | 68 |

| 4-2  | Our exploration methodology consists of two design decisions: data partitioning and cache reconfiguration.                                                                                                                                                                        | 71  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

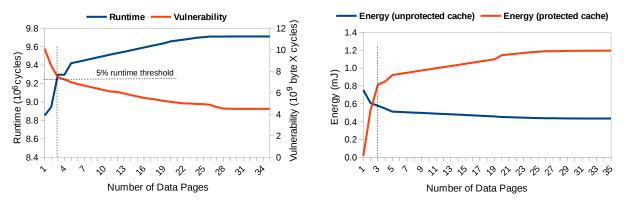

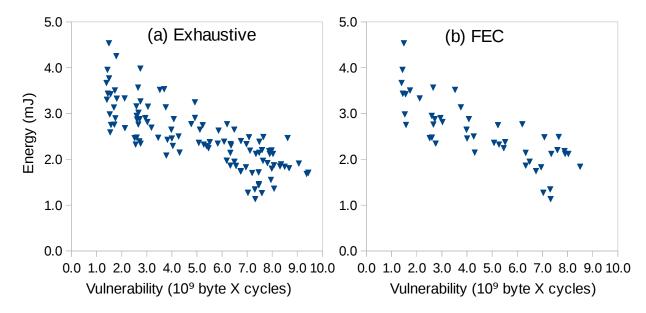

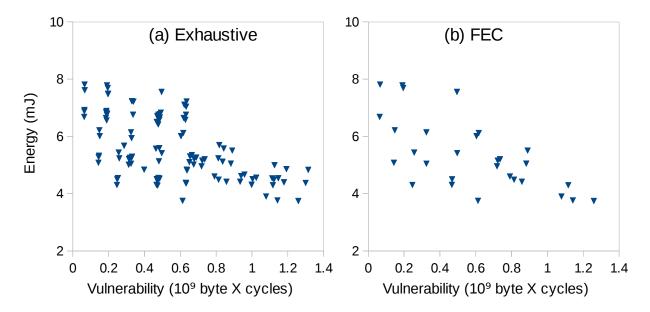

| 4-3  | Trade-off between vulnerability, runtime and energy, for benchmark <i>cjpeg</i> . (a) Vulnerability and runtime trade-off, (b) Energy consumption.                                                                                                                                | 71  |

| 4-4  | Configurations covered by (a) Exhaustive Exploration (108), (b) FEC Exploration (41), for benchmark <i>cjpeg</i> .                                                                                                                                                                | 76  |

| 4-5  | Configurations covered by (a) Exhaustive Exploration (108), (b) FEC Exploration (29), for benchmark <i>pegwit</i> .                                                                                                                                                               | 77  |

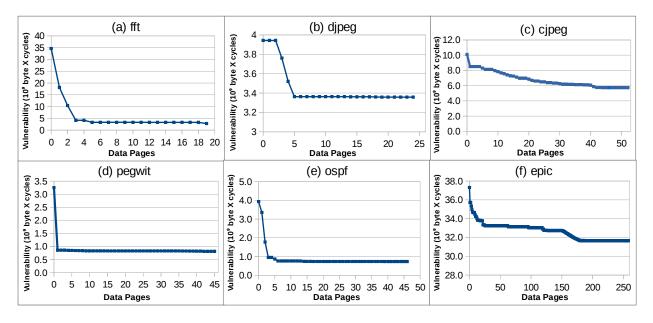

| 4-6  | Page exploration during data paritioning for six different benchmarks                                                                                                                                                                                                             | 77  |

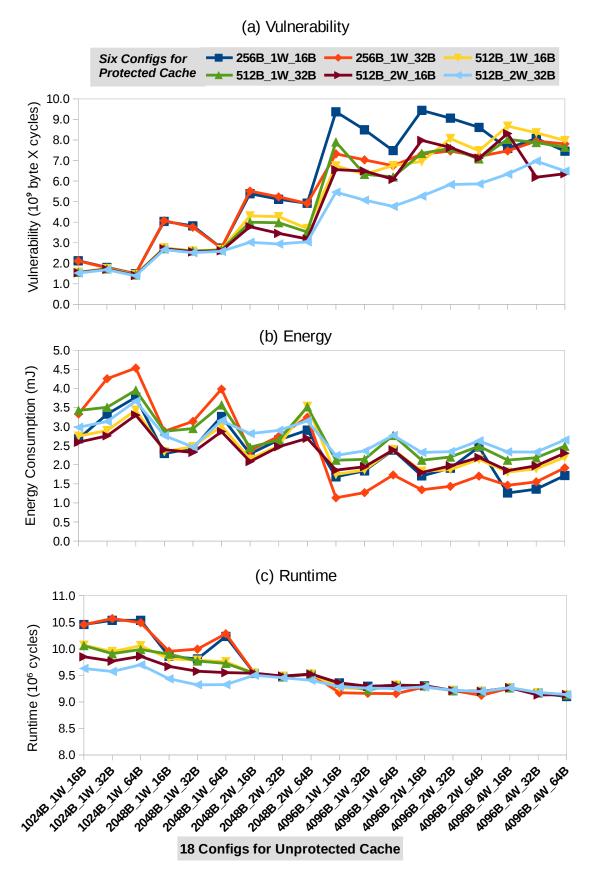

| 4-7  | Exploration of all cache configurations for benchmark $cjpeg$ , with $rThresh = 5\%$ .                                                                                                                                                                                            | 84  |

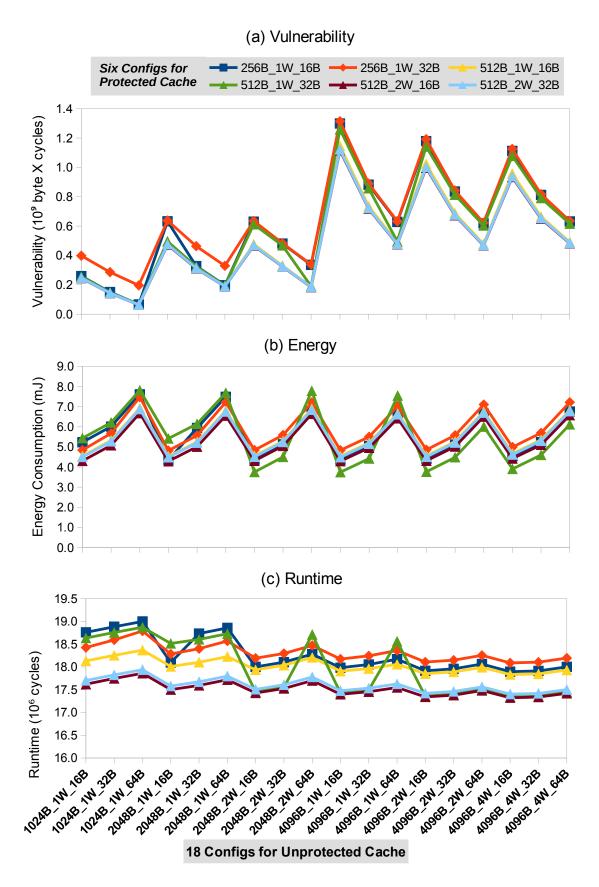

| 4-8  | Exploration of all cache configurations for benchmark $pegwit$ , with $rThresh = 5\%$ .                                                                                                                                                                                           | 85  |

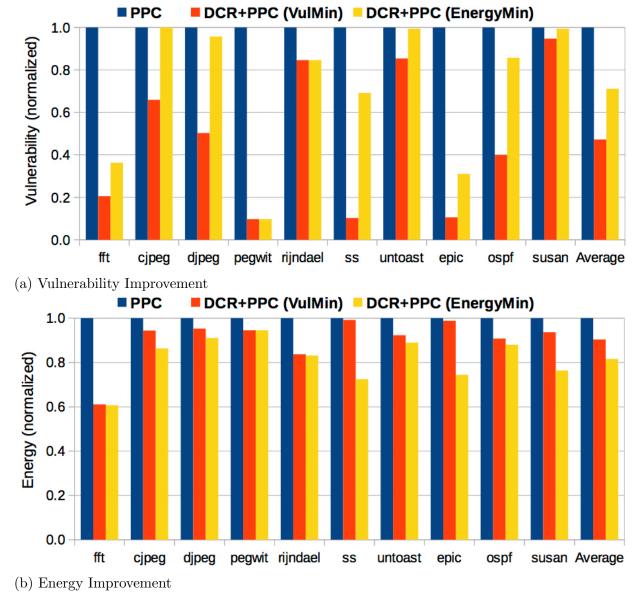

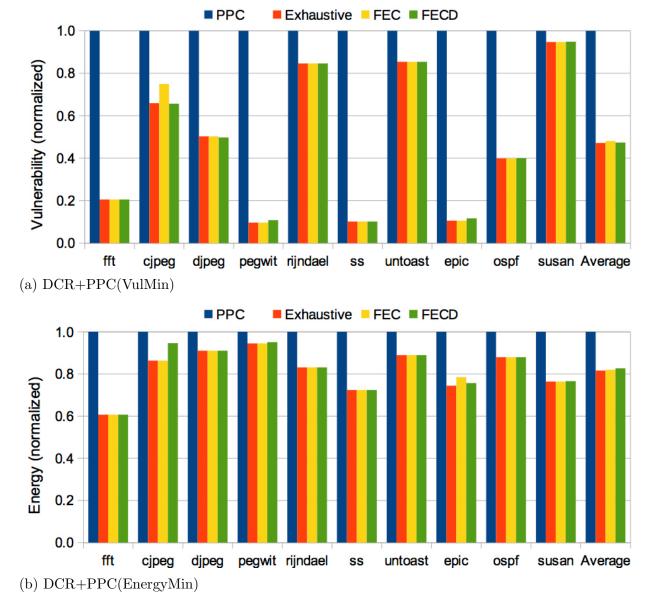

| 4-9  | Comparison of $DCR+PPC(VulMin)$ and $DCR+PPC(EnergyMin)$ with PPC[39]. (a) Vulnerability improvement, (b) Energy improvement.                                                                                                                                                     | 86  |

| 4-10 | Comparison of three exploration strategies: <i>Exhaustive</i> , <i>FEC</i> and <i>FECD</i> . (a) $DCR+PPC(VulMin)$ , (b) $DCR+PPC(EnergyMin) \dots \dots$                   | 90  |

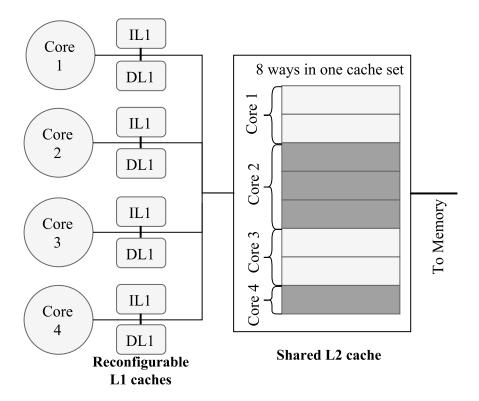

| 5-1  | A multicore system with reconfigurable L1 caches and a partition-enabled shared L2 cache.                                                                                                                                                                                         | 92  |

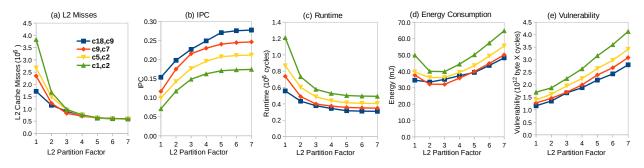

| 5-2  | Inter-dependence of L1 DCR and L2 CP on (a) L2 Misses, (b) IPC, (c)<br>Runtime, (d) Energy and (e) Vulnerability                                                                                                                                                                  | 93  |

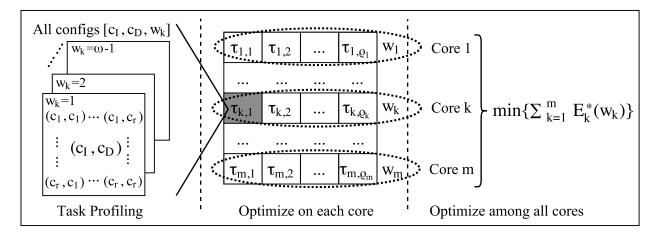

| 5-3  | Three-step optimization: the first step statically profiles each task, the second step optimizes for each partition factor on each core to find the best L1 cache configurations, the third step combines the optimal solution on all cores to find the best L2 partition scheme. | 97  |

| 5-4  | Recursive formula for dynamic programming                                                                                                                                                                                                                                         | 100 |

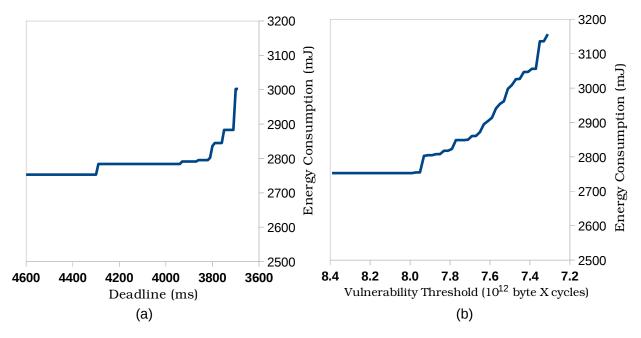

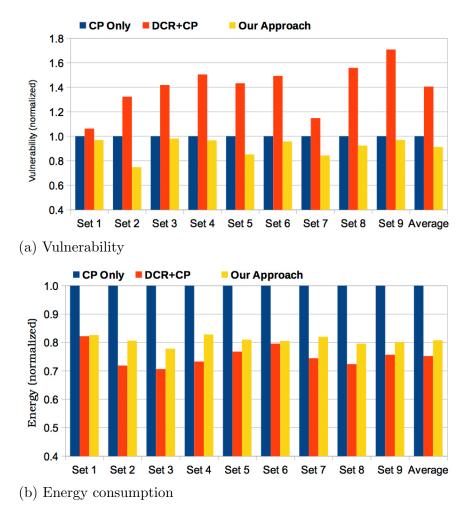

| 5-5  | Effects of Deadline and Vulnerability Threshold.                                                                                                                                                                                                                                  | 103 |

| 5-6  | Comparison of vulnerability and energy consumption for the cache hierarchy.<br>(a) Vulnerability, (b) Energy consumption.                                                                                                                                                         | 103 |

| 6-1  | Illustration of signal restoration for an AND gate                                                                                                                                                                                                                                | 113 |

| 6-2  | C Code Snippet for AES-128                                                                                                                                                                                                                                                        | 116 |

| 6-3  | An example showing the recovery of missing bits in $RK_{(4,4)}$ by using <i>sbox</i> lookup table (Rule 1).                                                                                                                                                                       | 121 |

| 6-4 | AES <i>sbox</i> lookup table (the numbers are in hexadecimal format) $\ldots \ldots \ldots$                                                                                                               | 122 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

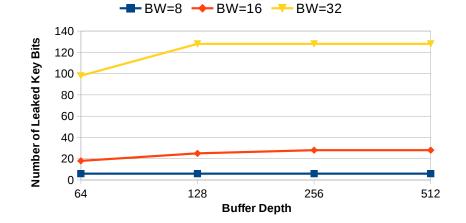

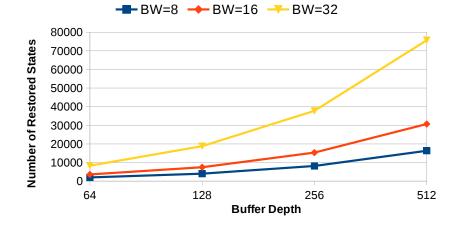

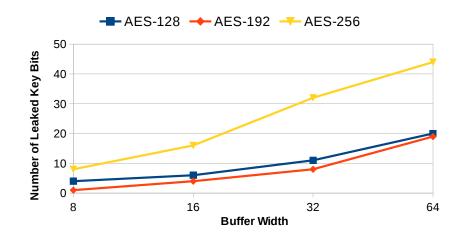

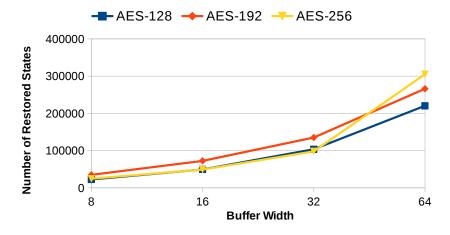

| 6-5 | Security and observability trade-off using different buffer widths and buffer depths.                                                                                                                     | 127 |

| 6-6 | Pipelined AES-128, AES-192, and AES-256 ciphers: security and observability trade-off.                                                                                                                    | 129 |

| 6-7 | LFSR-based Countermeasure                                                                                                                                                                                 | 131 |

| 6-8 | PUF-based Countermeasure                                                                                                                                                                                  | 131 |

| 7-1 | Trojans with rare nodes as trigger conditions. The 4-trigger Trojan will only be activated by the rare combination 1011 and the 8-trigger Trojan will only be activated by the rare combination 10110011. | 136 |

| 7-2 | Test generation framework for side-channel analysis based Trojan detection. $\ .$ .                                                                                                                       | 143 |

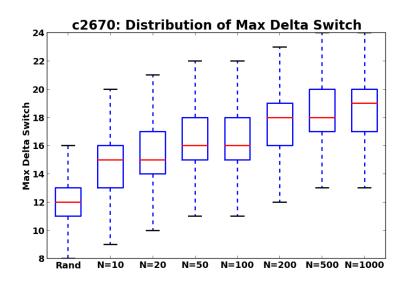

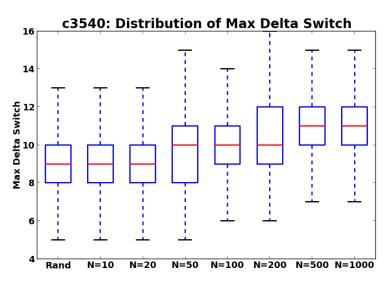

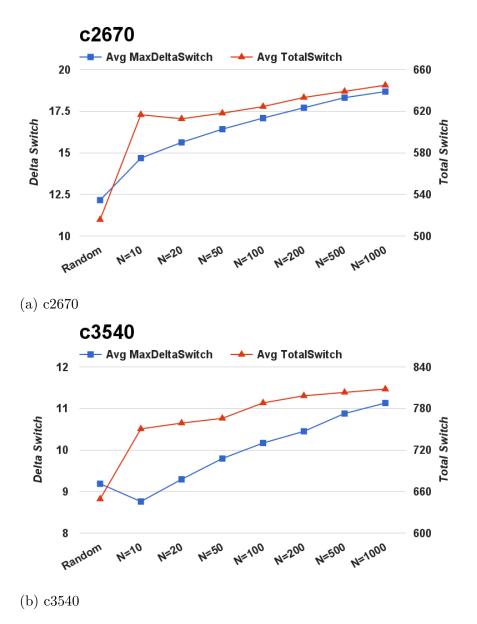

| 7-3 | Impact of N (number of times that a rare node have rare switching) on MaxDeltaSwitch for benchmarks (a) c2670 and (b) c3540.                                                                              | 145 |

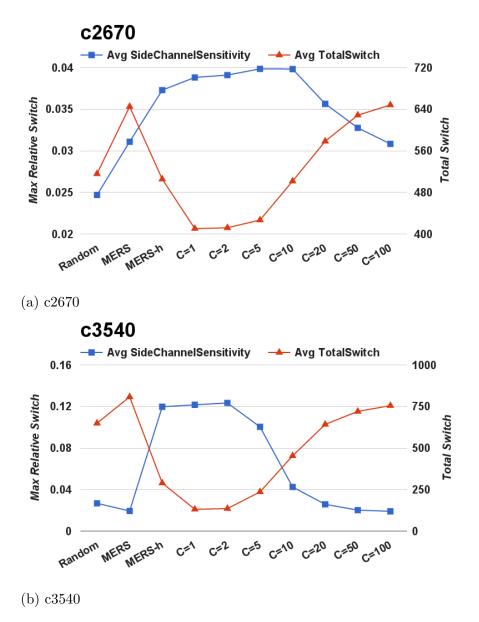

| 7-4 | MaxDeltaSwitch versus TotalSwitch for different N for benchmarks (a) c2670 and (b) c3540.                                                                                                                 | 147 |

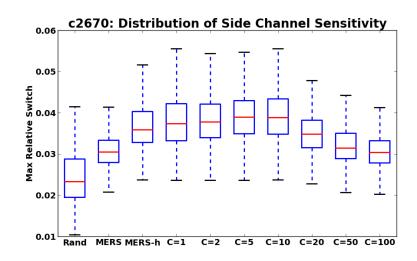

| 7-5 | Side Channel Sensitivity versus Total Switch for Random, the original MERS, MERS-h and MERS-s (with different $C$ ) for benchmarks (a) c2670 and (b) c3540.                                               | 148 |

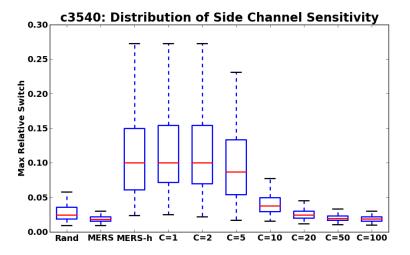

| 7-6 | Distribution of Side Channel Sensitivity for Random, the original MERS,                                                                                                                                   |     |

MERS-h and MERS-s (with different C) for benchmarks (a) c2670 and (b) c3540. 149

## Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

## SYSTEM-ON-CHIP VULNERABILITY ANALYSIS AND MITIGATION TECHNIQUES

By

Yuanwen Huang

August 2017

## Chair: Prabhat Mishra Major: Computer Engineering

As Internet of Things (IoT) stretches into every aspect of our life, the IoT devices provide us with efficiency, convenience and economic benefits. The IoT devices typically contain a System-on-Chip (SoC) computing platform. However, more and more vulnerabilities are discovered in SoCs, which suggests the urgent need of research to analyze and mitigate these vulnerabilities. This dissertation focuses on the hardware vulnerabilities of SoCs, which includes the memory vulnerability due to soft errors, the vulnerability of debug infrastructure, and malicious hardware implantation in integrated circuits. My research has made five major contributions: (i) it analyzes vulnerability of cache due to soft errors, and proposes scheduling-aware cache reconfiguration algorithms to reduce vulnerability for single-core systems; (ii) it proposes a reconfiguration approach for partially protected caches to mitigate cache vulnerability and reduce energy overhead; (iii) it proposes a cache reconfiguration strategy for multicore systems to reduce cache vulnerability; (iv) it analyzes the vulnerability of trace buffers, demonstrates that an attack can be mounted to steal the encryption key, and proposes countermeasures against this type of attack; (v) it analyzes the vulnerability due to hardware Trojans, and proposes statistical test generation algorithms for side-channel based Trojan detection. Experimental results suggest that the proposed approaches can significantly reduce hardware vulnerability to enable design of secure and reliable SoCs.

## CHAPTER 1 INTRODUCTION

The Internet of Things (IoT), defined as the infrastructure of the information society, is the network of physical devices embedded with electronics, software and network connectivity. As shown in Figure 1-1, IoT devices are pervasive in every aspect of our daily life. They enable us to have smart home, smart transport, smart finance, smart health, and so on. It is estimated that the IoT will consist of 50 billion objects by 2020 [1]. Safety, security and privacy concerns of IoTs have received significant attention from both academia and industry in recent years. Safety is a natural concern, since IoT devices and systems inherently have humans in the loop. People's lives depend on safety-critical devices, such as pacemakers and self-driving cars. The report by HP [2] indicates that 70% of the IoT devices have serious vulnerabilities. Many of these IoT devices are becoming easy targets for attackers. Privacy also becomes a concern, as many of the IoT devices have sensors to collect data from humans. It raises great concern regarding privacy of confidential personal information and health-related sensitive data.

Figure 1-1. The Internet of Things (IoT) is pervasive in every aspect of our daily life.

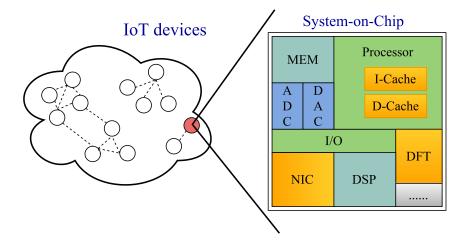

Figure 1-2. IoT devices typically contain a System-on-Chip (SoC) computing platform with reusable hardware IP components.

Majority of these IoT devices are designed using System-on-Chip (SoC) components and software applications [3]. In order to reduce design complexity as well as the time to market, SoCs use third-party Intellectual Property (IP) components. For example, Figure 1-2 shows a typical SoC with a processor core, a Digital Signal Processor (DSP), memory (MEM), analog-to-digital (ADC) and digital-to-analog (DAC) converters, network interface card (NIC), peripherals (I/O), design-for-test facility (DFT), and so on. In many cases, these IP components are designed by different companies across the globe. Each functional component may travel through long supply chain involving multiple vendors before they are integrated into a SoC. This design methodology of employing reusable hardware IPs severely affects the security and trustworthiness of SoC computing platforms, primarily due to three factors. (1) The third-party components might not be fully tested/verified under all conditions (such as corner-case inputs, extreme environment conditions). The reliability and availability of the SoC might be compromised when such a corner-case condition happens. (2) These SoCs may have undocumented test or debug interfaces that could be used as a backdoor for information leakage. (3) An SoC may come with malicious implants to incorporate undesired functionality (e.g. hardware Trojans).

### 1.1 Vulnerabilities in System-on-Chip

The top ten IoT vulnerabilities identified by the Open Web Application Security Project (OWASP) include [4]: insecure web interface, insufficient authentication or authorization, insecure network services, lack of transport encryption or integrity verification, privacy concerns, insecure cloud interface, insecure mobile interface, insufficient security configurability, insecure software or firmware, and poor physical security. These reported vulnerabilities mostly focus on analysis of the network/cloud and software/firmware holes in IoT devices. There are cases involving poor physical security, which is mostly gaining access to the software system through unprotected physical interfaces. There has not been much analysis of vulnerabilities of the underlying hardware itself. In this dissertation, we zoom into the underlying SoCs and investigate the hardware components for vulnerability analysis.

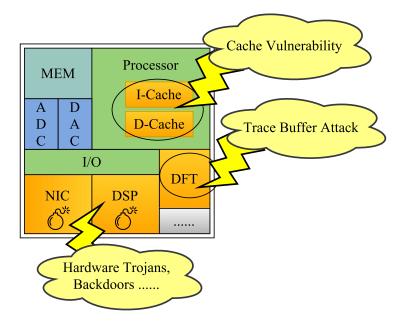

Figure 1-3. System-on-Chip vulnerabilities.

Vulnerabilities of a SoC come from its hardware IP components. According to the weakest-link theory, a SoC system is as vulnerable as the most vulnerable component. It is therefore important to verify each hardware component thoroughly before integrating them into a SoC. As shown in Figure 1-3, we have illustrated three possible vulnerabilities

that pose threats to the reliability and security of the SoC. Assume the caches in the processor have no protection against corrupted data (for example, a flipped bit). This error in caches may propagate and cause the whole system to crash. As for the Design-for-Test (DFT) module, the debugging information stored in the trace buffer could be used by attackers as a source of information leakage. We have shown a successful attack mounted to the trace buffer to steal the AES encryption key. Assume that the Network Interface Card (NIC) module and Digital Signal Processing (DSP) module are from untrusted third-party vendors, malicious implantations (such as hardware Trojans and backdoors) might be inserted for tampering the SoC or leaking information. In this dissertation, we focus on these three types of hardware vulnerabilities in SoCs. Analysis and mitigation techniques are proposed to improve the reliability and security of SoCs.

#### 1.2 Challenges

In this dissertation, three aspects of hardware vulnerability analysis are covered: (1) vulnerability of cache cells due to soft errors; (2) vulnerability of trace buffer used in hardware debugging; (3) vulnerability introduced by malicious implantations in integrated circuits. The following section describes the challenges concerning these vulnerabilities.

### **1.2.1** Vulnerability Due to Soft Errors

Soft errors are transient faults in CMOS circuits, which are caused by energy carrying particles (cosmic rays or substrate alpha particles). These transient faults flip bits in storage cells or change the logic values in functional units. Soft error rate per chip is expected to grow due to the growing density of transistors on chip [6].

Previous studies have concluded that unprotected memory elements are the most vulnerable components to soft errors [7]. The cache in embedded microprocessors is most susceptible to soft errors for several reasons: (i) cache occupies the majority of chip area, (ii) cache has an extremely high density of transistors, and (iii) cache cell size scales down, which reduces the critical charge needed to flip a bit in stored data. Due to widespread use of embedded systems in safety-critical devices, it is necessary to protect embedded caches from soft errors.

Detection and correction of soft errors in logic circuits usually involve the techniques of fault tolerant design. These include the use of redundant circuitry, such as triple modular redundancy (TMR). In this technique, three identical copies of a circuit are employed to compute on the same data in parallel and the result would be the value occurred in at least two of the three cases. In this way, the failure of one circuit due to soft error is discarded if the other two copies of the circuit work correctly. However, it will come at 200% overhead in circuit area and power, which is unacceptable in many cases. Another concept of temporal (or time) redundancy uses one circuit on the same data and checks consistency between several repetitive executions. This approach is more efficient than the modular redundancy approach, although it still incurs performance and power overhead. In this dissertation, we propose several cache reconfiguration techniques to mitigate vulnerability due to soft errors, with negligible impact on power and performance.

## 1.2.2 Vulnerability Due to Hardware Debug Infrastructure

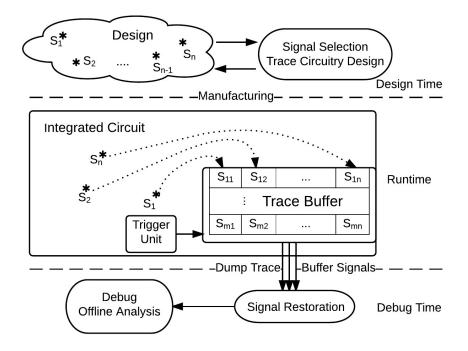

One of the major challenges in post-silicon validation and debug is the limited controllability and observability of the fabricated integrated circuit. Trace buffer is widely used to improve the observability of circuit and thus assist post-silicon debug and analysis. It is a buffer that traces (records) some of the internal signals in a silicon chip during runtime. If an error is encountered, the content of trace buffer would be dumped out through JTAG interface for off-line debug and error analysis. Due to design overhead constraints, the number of trace signals is only a small fraction of all internal signals in the design. The size of the trace buffer directly affects the observability that we can get from the trace buffer.

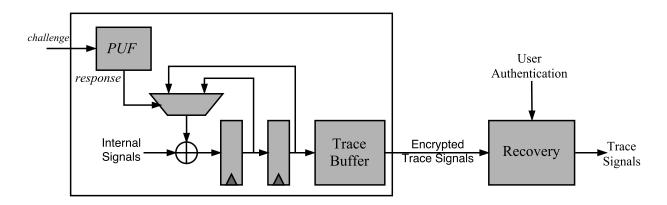

Figure 1-4 illustrates how the trace buffer is used during post-silicon validation and debug. Signal selection is done during the design time (pre-silicon phase). Let us assume that  $S_1, S_2, ..., S_n$  are the selected trace signals. Figure 1-4 shows a trace buffer with a

17

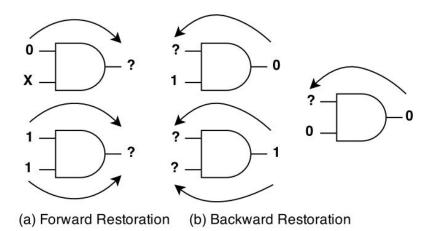

Figure 1-4. Overview of trace buffer in system validation and debug

total size of  $n \times m$  bits, which traces n signals (buffer width) for m cycles (buffer depth). For example, the ARM ETB [62] trace buffer provides buffer sizes ranging from 16Kb to 4Mb. In this case, a 16Kb buffer can trace 32 signals for 512 cycles (i.e., n=32 and m=512). Once the trace signals are selected, they need to be routed to the trace buffer. A trigger unit is also needed that decides when to start and stop recording the trace signals based on specific (error) events. The trace buffer records the states of the traced signals during runtime. During debug time, the states of traced signals are dumped out through the standard JTAG interface. Signal restoration is performed to restore as many states as possible, which tries to maximize the observability of the internal signals in the chip. The off-line debug and analysis are based on the traced signals and the restored signals.

System-on-Chip (SoC) designs have in-built trace buffer that traces a small set of internal signals during execution, and the traced signal values are used during post-silicon (off-line) debug. There is an inherent conflict between security and observability. While debug engineers would like to have better observability, the security experts would like to enforce limited or no visibility with respect to the security modules in a SoC design. A trade-off is typically made where trace signals are carefully selected to maintain security while providing reasonable debug capability. To the best of our knowledge, the vulnerability of trace buffers in cryptographic implementation has not been studied in the literature.

In practice, one routinely faces a situation where the cryptographic schemes are deployed in different adversarial setting, where keys are compromised, and the internal memory is not fully opaque. This situation leads to a set of physical cryptanalysis techniques, commonly known as *side channel attacks*. Side channel attacks exploit the physical implementation of cryptographic algorithms. The physical implementation might enable *leakage*, i.e., observations and measurements on the implementation details, as well as tampering with them. Trace buffer in post-silicon can provide observability into the hardware implementation, which implies that it can be employed as a source of information leakage by attackers.

### 1.2.3 Vulnerability Due to Malicious Implantation

Hardware Trojan attacks relate to malicious modifications in the design of integrated circuits (ICs) at different stages of the design or fabrication process [100][103][105]. An adversary can introduce these modifications in a design in order to cause disruption in normal functional behavior and/or to leak secret information from a chip during operation in field. Increased globalization of IC design and fabrication process coupled with reduced control on these steps by a trusted manufacturer makes the ICs highly vulnerable to these attacks. Since the threat of hardware Trojan in the form of a malicious implant in a design came into light about a decade ago through an US Department of Defense announcement [97], it has triggered wide array of research activities in threat analysis as well as design/validation solutions to evaluate this threat and protect against it. Hardware Trojan attacks are also being increasingly recognized in the semiconductor industry as a serious security concern.

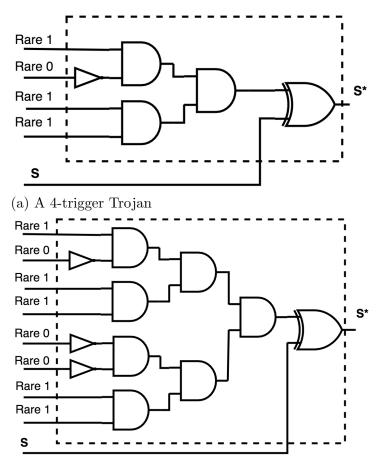

A Trojan is expected to be covert and difficult to detect, i.e. an intelligent adversary will likely insert a Trojan circuit in a way that evades detection during post-manufacturing functional/parametric testing, but manifests itself during long hour of in-field operation. This can be achieved by externally triggering its operation or by making it dependent on rare circuit conditions inside an IC. The condition of Trojan activation as commonly referred to as *trigger condition*, which can be purely combinational or sequential, related to the clock or a sequence of rare events in the state elements (e.g. flip-flops of registers). The internal circuit nodes affected by a Trojan activation are referred to as *payload* of a Trojan. Fig. 1-5 shows some example Trojan circuits including a combinational and a sequential Trojan. For example, a Trojan circuit could be triggered only when a data bus attains a unique rare value or when the number of times it attains the rare value equals a particular count. The malicious effects of Trojan payloads can range from passive, such as leakage of secret information to altering the original functionality of the chip in a critical or destructive fashion.

Protection against hardware Trojan attacks can be accomplished in two broad ways: (1) design-for-security techniques that make Trojan insertion difficult or make a Trojan easily detectable through post-silicon testing; and (2) manufacturing test approaches that aims at detecting an arbitrary Trojan by observing its effect into a circuit's operational behavior. The first class of techniques, primarily relies on different types of hardening approaches - e.g. insertion of dummy cells into empty spaces in a circuit layout; or key-based obfuscation of a design that make malicious alteration by an adversary provably hard. Design techniques, however, come at the cost of additional design, verification, and test time, as well as additional design overhead. For example, key-based obfuscation, even though is capable of providing high level of robustness against Trojan attacks, come at a cost of 10% or more area overhead [98]. More importantly, design solutions, however, only work for new designs and not legacy designs, and hence has limited applicability. Hence, efficient test/validation approaches that can provide high level of confidence regarding IC

20

(b) Sequential Trojan

Figure 1-5. Example of a combinational and a sequential Trojan with triggers from two rare internal nodes A and B.

trustworthiness in the presence of Trojan threat provides an attractive solution to the IC manufacturers.

Existing test solutions for hardware Trojan detection can be broadly classified into: 1) logic testing and 2) side-channel analysis approaches. In logic testing approach, directed structural or functional tests are generated to activate rare events in the circuit and propagate the malicious effect in logic values to primary outputs. Such approaches are known to be more effective in detecting ultra-small Trojans (typically a few gates in size) reliably under large process variations. The main challenge with logic testing approaches, however, is the difficulty to trigger a Trojan and observe its effect, particularly the complex sequential Trojans, and the inordinately large number of possible Trojan instances an adversary can exploit. On the other hand, side-channel analysis approaches, which depend on measurement of physical "side-channel" parameters like power signature of an IC in order to identify a structural change in the design. Such approaches have the advantage that they do not require triggering a malicious change and observing its impact at the primary output. Side-channel analysis (SCA) - primarily based on supply current has been extensively investigated by large number of research groups and various solutions to increase the signal-to-noise (SNR) has been proposed. A disadvantage of SCA is in terms of large process variations which can potentially mask the minute effect of a Trojan in the measured side-channel parameter e.g. 20X leakage power and 30% delay variations in 180nm technology [99].

A solution to the sensitivity problem can be achieved by judicious test generation approach that aims at maximizing the sensitivity for an arbitrary Trojan in unknown circuit location. To maximize sensitivity of a given Trojan, one needs to amplify activity inside the Trojan circuit and simultaneously minimize the background activity (i.e. activity in the original circuit). However, since the number of possible Trojan instances in a design can be inordinately large, a deterministic test generation method similar to conventional stuck-at fault test generation, cannot work. To address this issue, in this dissertation, we present a novel test generation framework that can maximize the detection sensitivity for an arbitrary Trojan.

#### **1.3** Research Contributions

My research proposes novel techniques to address vulnerability challenges described in Section 1.2. The objective of my research is to identify/analyze vulnerabilities and design efficient tools and techniques to mitigate these vulnerabilities in SoCs. The proposed research focuses on three major directions of hardware vulnerabilities: (1) the vulnerability due to soft errors, induced by high-energy particles hitting the microchip; (2) the vulnerability due to the exploitation of hardware debug infrastructure; (3) the vulnerability due to malicious implantations (hardware Trojans).

Figure 1-6 outlines the major research contributions of the dissertation that are summarized as follows.

- Vulnerability-aware Cache Reconfiguration: This dissertation examines the vulnerability issue of cache cells due to soft errors. The proposed approach exploits dynamic reconfiguration of embedded caches in multitasking soft real-time systems. By profiling each task with its optimal cache configurations statically, and dynamically selecting configurations at runtime, our approach can reduce vulnerability as well as energy consumption.

- Vulnerability-aware Reconfiguration for Partially Protected Caches: This dissertation proposes a reconfigurable cache architecture with the partially protected caches. The research combines the advantage of cache reconfiguration, which is favourable for energy and performance, and the advantage of partially protected caches, which is favourable for vulnerability reduction. The proposed approach synergistically explores data partitioning schemes and cache configurations to achieve both vulnerability reduction and energy improvement with minor impact on performance.

- Vulnerability Reduction for Multicore Systems: This dissertation proposes a cache reconfiguration approach for multicore systems to reduce vulnerability. The proposed approach uses dynamic reconfiguration of the private L1 caches and static partitioning of the shared L2 cache. Each task for each core is statically profiled. The optimal configurations for L1 caches and partition factors for L2 can be determined by a dynamic programming algorithm.

- **Debugging Infrastructure Vulnerability:** This dissertation analyzes the vulnerability of debugging infrastructure, specifically the trace buffer used in post-silicon debug. We investigate the trace buffer as a source for information leakage. Our proposed approach is able to mount an attack on different implementations of the AES ciphers through the help of trace buffer. Unless proper countermeasure is taken, the proposed attack can steal part of the key from the AES chip.

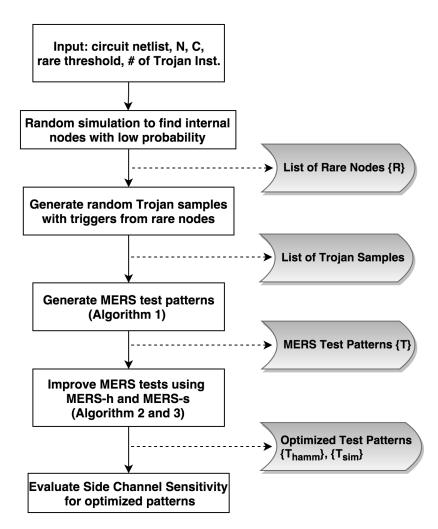

- Vulnerability due to Malicious Implantation: This dissertation surveys the pros and cons of test generation and side-channel analysis in detecting malicious implantations (hardware Trojans). I propose a novel side-channel-aware test generation approach, based on a concept of Multiple Excitation of Rare Switching (MERS). The tests generated by the proposed approach can significantly increase the Trojans sensitivity, thereby making Trojan detection effective using side-channel analysis.

The rest of this dissertation is organized as follows. Chapter 2 describes relevant

background and related work. Chapter 3 presents the vulnerability-aware cache

reconfiguration technique in single-core multitasking systems. Chapter 4 describes

the synergistic exploration of data partitioning and cache reconfiguration for partially

Figure 1-6. Dissertation Outline

protected caches. Chapter 5 presents the cache reconfiguration approach for multicore systems to reduce cache vulnerability. Chapter 6 analyzes the vulnerability of trace buffers and presents an attack on the Advanced Encryption Standard (AES) cipher. Chapter 7 presents a statistical test generation approach for side-channel based Trojan detection. Chapter 8 concludes the dissertation.

## CHAPTER 2 BACKGROUND AND RELATED WORK

This chapter surveys existing System-on-Chip vulnerability analysis and mitigation techniques. For ease of presentation, we have divided the existing approaches into three categories. First, we describe the existing techniques for cache vulnerability reduction. Next, we discuss existing research on security vulnerabilities in post-silicon debug. Finally, we present vulnerability due to hardware Trojans and associated detection techniques.

## 2.1 Dynamic Cache Reconfiguration for Vulnerability Reduction

This section is organized as follows. First, we describe how to compute vulnerability of caches. Next, we present existing cache reconfiguration techniques. Finally, we highlight the importance of partially protected caches for vulnerability reduction.

### 2.1.1 Cache Vulnerability

Soft errors are transient faults in CMOS circuits, which are caused by energy carrying particles (cosmic rays or substrate alpha particles). These transient faults flip bits in storage cells or change the logic values in functional units. Soft error rate per chip is expected to grow due to the growing density of transistors on chip [6]. Previous studies have concluded that unprotected memory elements are the most vulnerable components to soft errors [7]. According to [29], DRAMs have soft error rate (SER) of 1000 FIT, while SRAMs have SER of 100000 FIT (1 FIT is 1 failure in one billion device hours). Soft error rate of SRAM is significantly higher than that of DRAM [29, 31, 32]. The cache in embedded microprocessors is most susceptible to soft errors for several reasons: (i) cache occupies the majority of chip area, (ii) cache has an extremely high density of transistors, and (iii) cache cell size scales down, which reduces the critical charge needed to flip a bit in stored data. Due to widespread use of embedded systems in safety-critical devices, it is necessary to protect embedded caches from soft errors.

Major reliability improvement techniques include error correction and error prevention [6], [16], [19]. Error correction techniques, such as parity caching and error-correcting codes (ECC), use spatial redundancy to detect errors. If an error is detected in a cache block and this block is not dirty (i.e. memory has a correct copy of this block), it is possible to recover by reloading from memory. But if an error is detected in a dirty block, there is no way to recover the corrupted data. An important idea in protecting cache data from soft errors is to ensure that there is an updated copy of all cached data in memory (so data can be reloaded if soft error corrupts data). Even when caches have error detection or correction techniques, the detection/correction process comes at a cost. It consumes multiple clock cycles to correct the error and the CPU might get stalled to re-fetch the data if the error cannot be successfully corrected by ECC. To combat the data vulnerability due to soft errors, error correction codes (ECC) are used in lower levels of the memory hierarchy. However, ECC might not be suitable for caches because of short access time constraints [43]. Error prevention techniques [20], such as periodic flushing and early write-back, are introduced. However, too many memory-writes will keep the data-bus busy, which results in longer cache-miss latency and decreased overall performance. Particularly, write-through caches will always write data all the way to memory, but may not be a good idea for embedded systems. Moreover, too many data accesses will also consume a lot more energy than write-back caches. These hardware techniques need extra hardware support in cache, and are not sensitive to the data access pattern of the applications. In this dissertation, we assume no error prevention, as we aim to reduce vulnerability with the given reconfigurable cache architecture using Dynamic Cache Reconfiguration (DCR). Our approach for vulnerability reduction can work on top of any error correction or error prevention techniques. Our goal is to take advantage of the reconfigurable cache and the data access pattern of applications to reduce vulnerability and improve energy efficiency while meeting task deadlines.

In order to facilitate reliability analysis of cache, a measurement method is needed for the quantification of cache vulnerability due to soft errors [15]. Mukherjee et al. [17] introduced the concept of Architectural Vulnerability Factor (AVF). Vulnerability analysis

Figure 2-1. Vulnerable intervals of two data elements in cache (where W=Write Access, R=Read Access, E=Evict). (a) data with both *write* and *read* accesses; (b) data with only *read* accesses.

divides a bit's lifetime into vulnerable and un-vulnerable intervals [17, 18]. A bit is vulnerable for an interval, if soft errors that happen in this interval cause the program to get contaminated data. Similar to [17] and [21], we measure the vulnerability of cache on a per-byte basis. Activities during the lifetime of a byte includes "idle", "read", "write" and "eviction". Figure 2-1(a) shows a data with both read and write accesses, and the vulnerable intervals are marked by two black rectangles: the data is vulnerable between the first write and the second read as well as between the second write and the evict. During these two intervals, the data is read for reuse, while a flipped bit can corrupt the data, causing the program to use the corrupted cache data. The interval between the second *read* and the second *write* is un-vulnerable, since the data will be updated by the write operation even if soft errors corrupt it. The duration between the last (third) read and evict is also vulnerable, since this is dirty (modified) data and needs to be written back to memory. Therefore, any bit flip in this duration will result in corrupted data being written back to memory. Figure 2-1(b) shows a data with only *read* accesses, and the intervals between *read* accesses are vulnerable. However, the interval between the last *read* and the *evict* is un-vulnerable, since data will not be reused or written back to memory. Byte Cycles is an widely used term for measuring cache vulnerability [7, 34]. We measure the vulnerability of cache as the summation of vulnerable intervals of all bytes. It can be

27

defined as follows:

Vulnerability =

$$\sum_{all \ bytes}$$

vulnerable time of byte;

## 2.1.2 Dynamic Cache Reconfiguration

Dynamic Cache Reconfiguration (**DCR**) is a widely studied method for optimizing energy and performance in embedded systems [8]. The basic idea of cache reconfiguration is that different programs have varying data and instruction access characteristics during execution (runtime) and DCR tries to find the optimal cache configuration for a given application (program). For example, we can improve performance by increasing cache size when a program needs a lot of data accesses. Similarly, we can save energy by shutting down a part of the cache if the program is not data-intensive. However, cache reconfiguration will also affect the vulnerability due to soft errors. A large cache size for a data-intensive program might have fewer cache misses and thus improve energy and performance efficiency, but it is also likely to increase the vulnerability of cache data because of longer data retention in the cache.

Applications have varied instruction and data access patterns, which means that they require different cache requirements in terms of cache size, line size, and associativity. If the cache configuration is tuned according to the need of the application, we can gain performance improvement and energy savings. Figure 2-2 illustrates that inter-task and intra-task DCR can improve overall performance by tuning cache size for a system with three tasks. We assume that cache size is the only tunable parameter of cache for the ease of illustration (line size and associativity remain the same). Figure 2-2(a) shows a traditional system using a fixed *base cache*<sup>1</sup>, whereas in Figure 2-2(b) each task uses its

<sup>&</sup>lt;sup>1</sup> **Base cache** refers to the cache used in typical real-time systems, which is chosen to ensure durable task schedules. Typically, *base cache* is the globally optimal cache configuration determined during design time for a set of tasks.

favorable cache configuration and the overall execution time is improved. In the traditional system with a fixed *base cache*, Task 1 starts execution at time  $t_0$ , Task 2 and Task 3 start at  $t_1$  and  $t_2$ , respectively. The fixed *base cache* has a 4096-byte cache size for all tasks. In inter-task (application-based) cache reconfiguration, DCR tunes the cache when a new task starts its execution. Assuming Task 1 is computation-intensive, we choose a smaller (2048-byte) cache to save energy, while the execution time will increase. Assuming Task 2 is data-intensive, we choose a larger (8192-byte) cache and its runtime is greatly improved. Figure 2-2(c) shows the effect of combining inter- and intra-task cache reconfiguration. By introducing intra-task reconfiguration, Task 1 can improve its performance if suitable configurations are applied to the four phases during execution. Assuming Task 2 has three phases, we set the cache to be large (8192-byte) for the first and third phase for performance consideration, and set the second phase to 4096-byte to reduce energy consumption. For Task 3, inter-task reconfiguration can find three phases and improve the performance and/or energy.

It is a major challenge to improve the reliability of real-time embedded systems with special design considerations of real-time constrains. Hard real-time systems require that all tasks must complete execution before their deadlines to ensure correct execution. A task set is considered schedulable if there exists a schedule that satisfies all the timing constraints. Due to stringent timing constraints, scheduling for hard real-time systems must perform task schedulability analysis based on task attributes (such as deadlines, priorities, and periods) [9]. For soft real-time systems, minor deadline misses may result in temporary service degradation, but will not lead to incorrect behavior. An efficient cache reconfiguration framework is proposed for energy optimization in soft real-time systems in [8]. They exploit the flexibility of soft real-time systems and manage to achieve considerable energy savings with minor impact on user experiences. However their method does not consider the vulnerability of cache due to soft errors.

29

Figure 2-2. DCR in a system with three tasks.

DCR has been extensively studied by previous works [8], [10], [11], [12], [13]. Reconfigurable cache architectures are extensively studied in [49]. Gordon-Ross et al. [50] utilizes DCR to improve performance by online feedback and dynamic self-tuning of the cache. An energy-efficient approach using DCR is proposed in [11] for soft real-time systems using static profiling and dynamic reconfiguration. DCR in two-level cache hierarchy in uniprocessor has been studied by [47]. DCR for multicore systems has been studied by [13] for thread-fairness and performance improvement. Wang et al. proposed an energy-efficient approach for multicore systems in [12] by using DCR on private L1 caches and cache partitioning (CP) on the shared L2 cache. CP is a special case of reconfiguration on the shared cache among multiple cores [51, 52]. Initial works of CP aim at improving the performance of multicore systems [52, 53]. Reddy et al. investigates energy-efficient CP for multitasking embedded systems in [54]. However, none of the above approaches takes vulnerability into consideration. Cai et al. [14] is the first attempt to consider the effect of cache configurations for energy and vulnerability in time-constrained systems. Their approach only considers simple exploration of cache sizes.

In Chapter 3, we propose a vulnerability-aware DCR approach to explore performance, energy and vulnerability trade-offs in uniprocessor-based systems. In Chapter 5, we extend vulnerability-aware cache reconfiguration for multicore systems.

### 2.1.3 Partially Protected Caches for Vulnerability Reduction

Several microarchitectural techniques have been proposed to reduce the vulnerability of memory data due to soft errors. Error Correction Codes (ECC) is a popular technique used to detect the transient faults in memory and correct the corrupted data. The most common ECC uses Hamming codes that provide single bit error correction and double bit error detection (SEC-DED) [43]. Previous research shows that SEC-DED codes implementation can increase the cache access time by up to 95% [44] and power consumption by up to 22% [45]. While it might be possible to hide the performance overhead through hardware optimization, it is not possible to hide power/energy overhead.

The idea of Partially Protected Caches (PPC) initially comes from horizontally partitioned caches [40], where a processor has two or more caches at the same level of the memory hierarchy. Horizontally partitioned caches can help reduce cache pollution and thereby improve performance and/or energy consumption. Lee et al. [38, 39, 41] extends the idea of horizontally partitioned caches into the PPC architecture, by assuming that one of the two caches is protected from soft errors. The protected cache has redundancy logic like SEC-DED [43] for error protection, which has overhead in access time, area and power consumption [44, 45]. To align the access latency with the unprotected cache, the protected cache is typically smaller than the unprotected cache. PPC is expensive in terms of energy consumption and performance, compared to the original architecture with only an unprotected cache. PPC works very well for multimedia applications where the partition between vulnerable data and multimedia data (not so vulnerable) is very clear. It is a challenge to make PPC reduce vulnerability for general applications, while incurring acceptable performance and energy penalty. In other words, designers would like to use PPC to reduce vulnerability but cannot afford significant increase in both execution time and energy consumption.

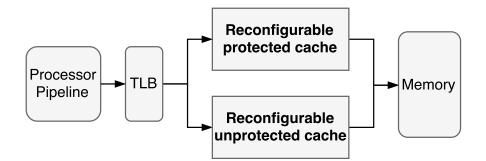

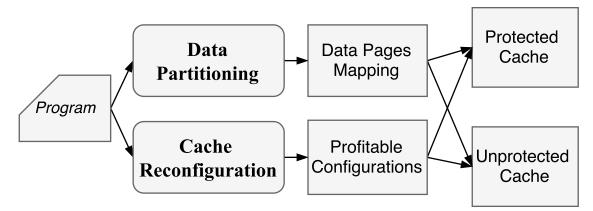

Figure 4-1 shows that the PPC architecture protects one cache from soft errors, while keeping the other cache unprotected. Each page from the memory is exclusively mapped into one of the two caches. Pages have a mapping attribute set by the compiler, which indicates the cache where a specific page should be mapped. When a new page is requested by the processor, the Translation Look-aside Buffer (TLB) will be checked to figure out which cache has the data. Therefore, only one cache will be accessed for each data access. Every time data is written into the protected cache, the data needs to be encoded, and it needs to be decoded when data is read from the cache. The challenge of using PPC is to properly partition data into two caches to ensure that it would not introduce too much penalty in performance and energy consumption. Lee et al. [38] used PPC to mitigate soft error failures for multimedia applications by selective data protection. They partition the data into failure non-critical (multimedia data) and failure critical, and map them into the unprotected and protected caches, respectively. Their approach works well for multimedia applications since the separation of multimedia data and other data is relatively easy. In [41], Lee et al. presented a data partitioning method which can work for general applications. It exhaustively searches for data pages to map them into the protected cache to reduce vulnerability, while not violating the 5%performance penalty constraint. In [39], another data partitioning method is proposed to search possible mapping schemes with a greedy approach. However, the existing

32

approaches use PPC only for the purpose of reducing vulnerability, and these approaches can introduce unacceptable energy overhead. In Chapter 4, we propose a DCR approach using PPC architecture to enable reduction in both energy consumption and cache vulnerability.

## 2.2 Trace Buffer Attack on AES

Trace buffer provides observability into the circuit so as to assist post-silicon debug and test. The quality of selected trace signals directly affects the observability that we can get from the circuit. The goal of trace signal selection is to obtain a set of signals, which can restore the maximum number of internal states in the chip. Basu et al. [76] proposed a metric based algorithm that employs total restorability for selecting the most profitable signals. Chatterjee et al. [77] proposed a simulation based algorithm which is shown to be more promising than metric based approaches. Li and Davoodi [78] proposed a hybrid approach which combines the advantages of metric and simulation based approaches. A simulation based approach using augmentation and ILP techniques by Rahmani et al. [79] demonstrated very high restoration capability and thus high observability of the internal signals. It is accepted in the research community that there is a strong link between observability/testability and security [83] for Design for Testability (DfT) facilities. Scan chain based DfT has been studied for attacks on block ciphers, including Data Encryption Standard (DES) [84] and Advanced Encryption Standard (AES) [85], and stream ciphers [86]. However, it is surprising that the vulnerability of trace buffers in cryptographic implementation has not been studied so far. This forms the core motivation of our work.

## 2.2.1 AES Specification

AES works on a block size of 128 bits and a key size of 128, 192 or 256 bits, which are referred to as AES-128, AES-192 and AES-256, respectively<sup>2</sup>. We briefly review AES-128 here, for further details readers can refer to [61].

Figure 2-3. AES Encryption Flow

The encryption flow of AES is shown in the Figure 2-3. AES accepts a 128-bit plaintext, 128-bit user key and generates 128-bit ciphertext. The encryption proceeds through an initial round and subsequent 10 round repetition of 4 steps. These steps are *SubBytes, ShiftRows, MixColumns* and *AddRoundKey*. In the final round, MixColumns step is skipped. For each of these rounds, separate 128-bit round subkeys are needed. The round subkeys are generated from the initial user key via a key expansion step. The key expansion uses Rijndael's key schedule.

$<sup>^2</sup>$  For the rest of the chapter, unless explicitly specified, we will use AES-128 and AES interchangeably.

The plaintext is organized as a  $4 \times 4$  column-major order matrix, which is operated through the AES rounds. The SubBytes step uses a non-linear transformation on every element of the matrix. The non-linear transformation is defined by an 8-bit substitution box, also known as Rijndael S-box. The ShiftRows step cyclically shifts the bytes in each row by a certain offset. In the MixColumns step, each column is multiplied by a fixed matrix. In the AddRoundKey step, each byte of the matrix is exclusive-OR-ed with each byte of the current round subkey. This is shown graphically in the Figure 2-3.

### 2.2.2 AES Attacks

Advanced Encryption Standard (AES) algorithm with various key lengths (128, 192 and 256) is widely used. The fact that AES stood the intense scrutiny from attackers over the last 15 years itself makes it an important benchmark for cryptography and cryptanalysis. So far, the best-known attempt against full AES-128, by *algebraic crypt-analysis*, has a computational complexity of  $2^{126.1}$ , which is slightly better than the brute-force attack and practically infeasible [59]. However, the perspective of *physical cryptanalysis* changes this scenario completely.

Since the pioneering works on differential power analysis [63], numerous side-channel attacks have been developed. Side-channel attacks can be classified into *passive, semiinvasive* and *invasive* attacks depending on the level of intrusion necessary for the attacker. The side-channels are of varied forms ranging from the software execution pattern such as cache timing [64] to more detailed hardware-oriented information leakages such as electromagnetic waves [65], acoustic waves [66] and optical fault injections [67]. Recent surveys on timing channels and invasive fault attacks are available in [68] and [69], respectively. Another approach of constructing an invasive attack originates from a malicious hardware, secretly inserted into a chip. These are commonly known as hardware Trojans [94, 95]. Such attacks have broken systems with mathematical security proof. In this scenario, secure implementation is rapidly becoming as important as the mathematical security proofs. For example, an AES implementation with protection against a first-order side-channel attack is presented in [60]. The protected design is still vulnerable to more sophisticated attacks and even then, incurs  $4.6 \times$  area- and  $3.6 \times$  power-overhead, respectively, compared to the unprotected implementation.

Considering the impact that AES has on our everyday communications, many of the attack techniques report their efficacy by demonstrating an attack on AES, which is also the target cipher for the current work. Among the hardware side-channel attacks reported against AES, attacks based on scan-chain [72] and external fault injections [73] are most prominent. For all these attacks, effective countermeasures are proposed and the inherent resilience of various design points [74] is studied. It is also shown that there exists an interplay between the countermeasures of one attack and the consequently increased vulnerability against another attack [75].

In Chapter 6, I propose a novel and effective attack, termed *Trace Buffer Attack*. It identifies the trace buffer as a source of information leakage and shows that an effective security attack on AES is possible by analyzing the trace buffer content.

### 2.3 Hardware Trojan Attacks and Detection Techniques