# EFFICIENT APPROACHES FOR FUNCTIONAL VALIDATION OF SOC DESIGNS USING HIGH-LEVEL SPECIFICATIONS

By MINGSONG CHEN

## A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# UNIVERSITY OF FLORIDA

2010

© 2010 Mingsong Chen

To my parents for their love and encouragement

#### ACKNOWLEDGMENTS

Although four years passed in a twinkling, all the vivid snapshots are deeply engraved in my memory. I always think that I was lucky to be a Gator in UF, not only because I witnessed four National Championships, but also I achieved another milestone in my life here. I need to confess that the journey to get a Ph.D. is challenging. It is impossible to imagine completing it without the precious advice and help from other people.

First of all, I really appreciate what my supervisor Dr. Prabhat Mishra did for me. His expertise and insights helped me to quickly capture the research direction and made this dissertation come true. Throughout my Ph.D. study, he gave me enduring support, guidance and encouragement which helped me to overcome various problems. There is no doubt that his attitude on research has deeply affected me and will be helpful in my future career. Finally I understood why he was always urging me to make progress. His efforts made my CV looks stronger which is beneficial to me.

I would also like to thank my Ph.D. committee members: Prof. Sartaj Sahni, Porf. Jih-Kwon Peir, Prof. Tao Li and Prof. Raymond Issa. Their valuable suggestions at different stages of my research were constructive and thought-provoking. Their criticisms enhanced the quality of my research. Colleagues and friends are an important part in my graduate life. I am very grateful for the friendship of all the members in my research group - Kanad Basu, Hadi Hajimiri, Heon-Mo Koo, Chetan Murthy, Kartik Shrivastava, Xiaoke Qin and Weixun Wang. I really enjoyed the harmonious atmosphere of our lab and the experience of collaborating with them.

Last but not least, I sincerely thank my parents, who unconditionally gave me the love and encouragement. Without their support, I won't reach this far. I dedicate this dissertation to them.

This work was partially supported by grants from Intel Corporation and NSF CAREER award 0746261.

4

# TABLE OF CONTENTS

|      |      | $\underline{\mathrm{pag}}$                        | ge |

|------|------|---------------------------------------------------|----|

| ACK  | NOW  | LEDGMENTS                                         | 4  |

| LIST | OF   | TABLES                                            | 9  |

| LIST | OF   | FIGURES                                           | 1  |

| ABS  | TRA  | CT                                                | 13 |

|      |      |                                                   | .0 |

| СНА  | PTE. | R                                                 |    |

| 1    | INTI | RODUCTION                                         | 14 |

|      |      |                                                   |    |

|      | 1.1  | 0                                                 | 15 |

|      | 1.2  | 0                                                 | 16 |

|      |      | 1.2.1 Overview of Functional Validation Methods   | 17 |

|      |      | 1.2.2 Potential Improvement Opportunities         | 18 |

|      |      | 1.2.3 Challenges                                  | 20 |

|      | 1.3  | Dissertation Contributions                        | 21 |

| 2    | FOR  | MAL MODELING OF SOC SPECIFICATIONS                | 23 |

|      |      |                                                   |    |

|      | 2.1  |                                                   | 24 |

|      |      |                                                   | 25 |

|      |      |                                                   | 27 |

|      |      | 2.1.2.1 Structure Extraction                      | 28 |

|      |      | 2.1.2.2 Behavior Extraction                       | 30 |

|      |      | 2.1.3 A Prototype Tool For TLM to SMV Translation | 32 |

|      | 2.2  |                                                   | 32 |

|      |      |                                                   | 33 |

|      |      |                                                   | 36 |

|      |      |                                                   | 10 |

|      |      |                                                   | ±0 |

|      |      |                                                   |    |

|      |      |                                                   | 12 |

|      | 0.0  |                                                   | 14 |

|      | 2.3  |                                                   | 15 |

|      |      | 1                                                 | 15 |

|      |      | 2.3.2 Example 2: A MIPS Processor                 | 16 |

|      |      | 2.3.3 Example 3: An Alpha Processor               | 17 |

|      |      | 2.3.4 Example 4: A Control System                 | 18 |

|      |      | 2.3.5 Example 5: A Stock Exchange System          | 18 |

|      | 2.4  |                                                   | 19 |

| 3 | COV | VERAGE-DRIVEN AUTOMATIC GENERATION OF DIRECTED TESTS                    | 50                         |

|---|-----|-------------------------------------------------------------------------|----------------------------|

|   | 3.1 | Coverage-Driven Property Generation                                     | 51<br>52<br>52<br>53<br>54 |

|   |     | 3.1.2 Functional Coverage Based on Fault Models                         | 55                         |

|   | 3.2 | Test Generation using Model Checking Techniques                         | 56                         |

|   |     | 3.2.1 Test Generation using Unbounded Model Checking                    | 56                         |

|   |     | 3.2.1.1 Unbounded Model Checking                                        | 56                         |

|   |     | 3.2.1.2 Test Generation Algorithm                                       | 57                         |

|   |     | 3.2.2 Test Generation using Bounded Model Checking                      | 57                         |

|   |     | 3.2.2.1SAT-Based Bounded Model Checking3.2.2.2Test Generation Algorithm | $57 \\ 58$                 |

|   |     | 3.2.2.2Test Generation Algorithm                                        | 58<br>59                   |

|   | 3.3 | Case Studies                                                            | 60                         |

|   | 0.0 | 3.3.1 A Control System                                                  | 61                         |

|   |     | 3.3.2 A Stock Exchange System (OSES)                                    | 62                         |

|   | 3.4 | Summary                                                                 | 63                         |

| 4 | PRO | OPERTY CLUSTERING FOR EFFICIENT TEST GENERATION                         | 64                         |

|   | 4.1 | Related Work                                                            | 65                         |

|   | 4.2 | Background: SAT Solver Implementation                                   | 66                         |

|   |     | 4.2.1 DPLL Algorithm                                                    | 67                         |

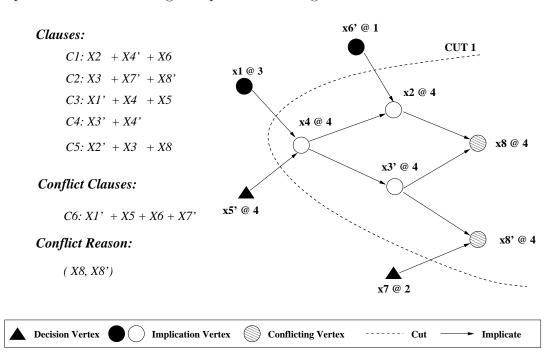

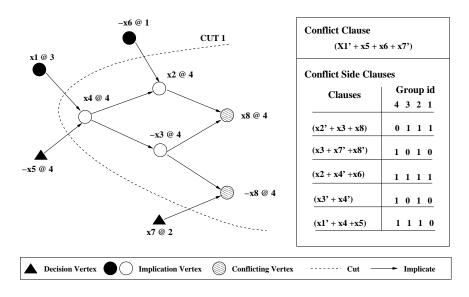

|   |     | 4.2.2 Conflict Clause Based Learning                                    | 67                         |

|   | 4.3 | Property Clustering                                                     | 70                         |

|   |     | 4.3.1 Similarity based on Structural Overlap                            | 72                         |

|   |     | 4.3.2 Similarity based on Textual Overlap                               | 73                         |

|   |     | 4.3.3 Similarity based on Influence                                     | 74<br>76                   |

|   |     | <ul> <li>4.3.4 Similarity based on CNF Intersection</li></ul>           | 76<br>76                   |

|   | 4.4 | 4.3.5 Determination of Base Property                                    | 70                         |

|   | 1.1 | 4.4.1 Conflict Clause Forwarding Techniques                             | 77                         |

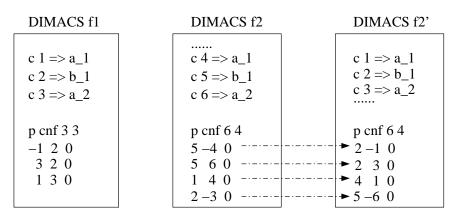

|   |     | 4.4.2 Name Substitution for Computation of Intersections                | 80                         |

|   |     | 4.4.3 Identification and Reuse of Common Conflict Clauses               | 81                         |

|   | 4.5 | Case Studies                                                            | 83                         |

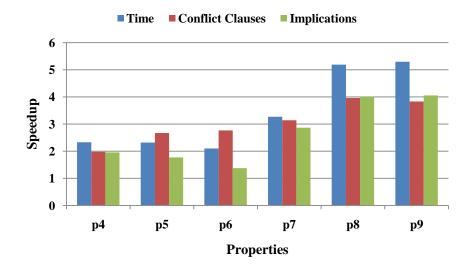

|   |     | 4.5.1 A VLIW MIPS Processor                                             | 84                         |

|   |     | 4.5.1.1 Structure-based Clustering                                      | 84                         |

|   |     | 4.5.1.2 Clustering based on Textual Similarity                          | 87                         |

|   |     | 4.5.1.3 Influence-based Clustering                                      | 88                         |

|   |     | 4.5.1.4 Intersection-based Clustering                                   | 89                         |

|   |     | 4.5.1.5 Comparison of Clustering Technques                              | 91<br>02                   |

|   | 1 C | 4.5.2 A Stock Exchange System                                           | 92<br>05                   |

|   | 4.6 | Summary                                                                 | 95                         |

| 5 | DEO | CISION ORDERING BASED INTRA- AND INTER-PROPERTY LEARNING                                                 | <b>G</b> 96 |

|---|-----|----------------------------------------------------------------------------------------------------------|-------------|

|   | 5.1 | Related Work                                                                                             | 97          |

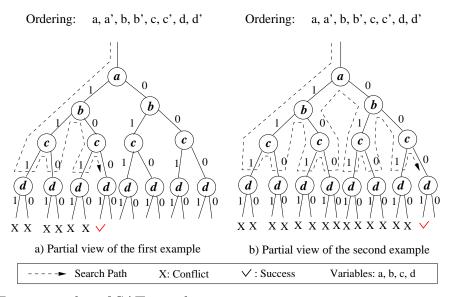

|   | 5.2 | Decision Ordering Based Learnings                                                                        | 97          |

|   |     | 5.2.1 Overview $\ldots$ | 98          |

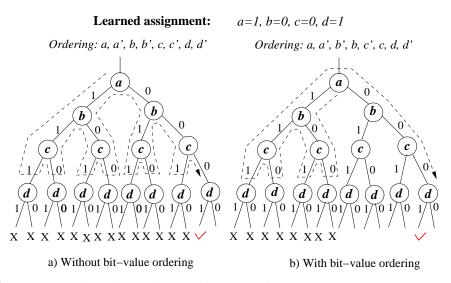

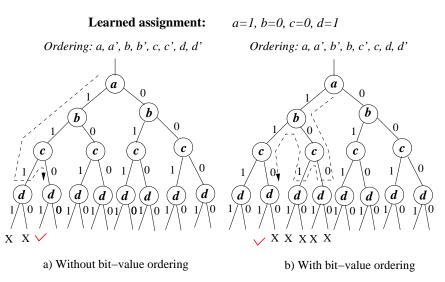

|   |     | 5.2.2 Bit Value Ordering                                                                                 | 99          |

|   |     | 0                                                                                                        | 101         |

|   |     |                                                                                                          | 102         |

|   | 5.3 | 8                                                                                                        | 103         |

|   |     |                                                                                                          | 104         |

|   |     | 1                                                                                                        | 105         |

|   |     |                                                                                                          | 106         |

|   |     | 1                                                                                                        | 107         |

|   |     | ·                                                                                                        | 108         |

|   | - 1 |                                                                                                          | 110         |

|   | 5.4 |                                                                                                          | 111         |

|   |     | 1 0 0                                                                                                    | 111         |

|   |     |                                                                                                          | 115         |

|   |     |                                                                                                          | 115         |

|   |     | $\mathbf{O}$                                                                                             | 118         |

|   | 5.5 | Summary                                                                                                  | 119         |

| 6 | EFF | FICIENT PROPERTY DECOMPOSITION TECHNIQUES                                                                | 120         |

|   | 6.1 | Learning-Oriented Property Decomposition                                                                 | 122         |

|   |     | 6.1.1 Potential Learnings for Complex Properties                                                         | 122         |

|   |     | 6.1.2 Spatial Property Decomposition                                                                     | 124         |

|   |     |                                                                                                          | 127         |

|   | 6.2 | 0 1                                                                                                      | 130         |

|   | 6.3 | 9                                                                                                        | 132         |

|   | 6.4 | 1                                                                                                        | 133         |

|   |     |                                                                                                          | 133         |

|   |     |                                                                                                          | 135         |

|   | 6.5 | 1                                                                                                        | 135         |

|   |     |                                                                                                          | 136         |

|   |     | 0                                                                                                        | 138         |

|   | 6.6 | Summary                                                                                                  | 139         |

| 7 | REU | USE OF VALIDATION EFFORT FOR ASSERTION-BASED EQUIVALENCE                                                 | E140        |

|   | 7.1 | Related Work                                                                                             | 142         |

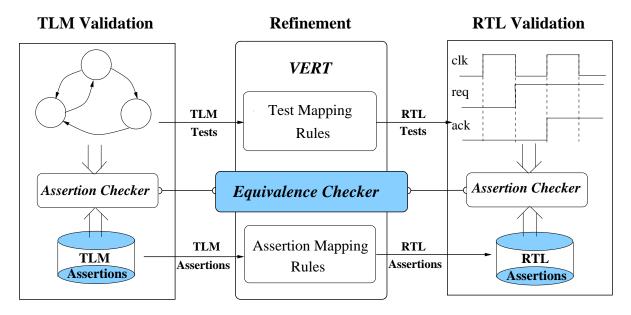

|   | 7.2 |                                                                                                          | 144         |

|   |     |                                                                                                          | 144         |

|   |     |                                                                                                          | 145         |

|   |     |                                                                                                          | 146         |

|   |     |                                                                                                          | 147         |

|     |     |        | 7.2.2.1   | Symbol Mapping 1                                | 48  |

|-----|-----|--------|-----------|-------------------------------------------------|-----|

|     |     |        | 7.2.2.2   | Assertion Refinement Rules                      | 48  |

|     |     |        | 7.2.2.3   | Test Refinement Rules                           | 50  |

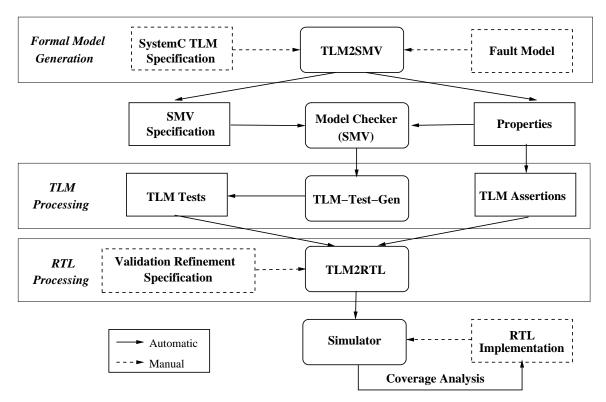

|     |     | 7.2.3  | A Protot  | ype Tool for TLM-to-RTL Validation Refinement 1 | 51  |

|     |     |        | 7.2.3.1   | TLM2SMV                                         | 52  |

|     |     |        | 7.2.3.2   | TLM Test Generation                             | 53  |

|     |     |        | 7.2.3.3   | TLM2RTL 1                                       | 53  |

|     |     | 7.2.4  | Assertion | n-Based Functional Equivalence                  | 54  |

|     |     |        | 7.2.4.1   | Assertion-Based Functional Coverage             | 54  |

|     |     |        | 7.2.4.2   | Assertion Ordering                              | 55  |

|     |     |        | 7.2.4.3   | Assertion Based Functional Equivalence          | 57  |

|     | 7.3 | Case S | Study .   |                                                 | 59  |

|     |     | 7.3.1  | A Route   | r Example                                       | 59  |

|     |     | 7.3.2  | A Pipelin | ned Processor Example                           | 64  |

|     | 7.4 | Summ   | ary       |                                                 | 65  |

| 8   | CON | ICLUS  | IONS AN   | D FUTURE WORK                                   | 66  |

|     | 8.1 | Conclu | isions .  |                                                 | .66 |

|     | 8.2 |        |           |                                                 | 67  |

|     |     |        |           |                                                 |     |

| REF | ERE | NCES   |           |                                                 | 69  |

| BIO | GRA | PHICA  | L SKETO   | СН 1                                            | 76  |

# LIST OF TABLES

| Tabl |                                                          | page |

|------|----------------------------------------------------------|------|

| 1-1  | A comparison for four optimizations                      | 20   |

| 2-1  | Break down of a token in Figure 2-8                      | 36   |

| 2-2  | Condition on the flow edges in Figure 2-8                | 36   |

| 3-1  | Comparison of two methods                                | 61   |

| 3-2  | Implementation level coverage of the control system      | 61   |

| 3-3  | Comparison of three methods                              | 62   |

| 3-4  | Implementation level coverage of OSES                    | 63   |

| 4-1  | Verification results for a structure-based cluster       | 85   |

| 4-2  | Structure-based clustering results for MIPS processor    | 86   |

| 4-3  | Verification results for a textual cluster               | 87   |

| 4-4  | Textual clustering results for MIPS processor            | 88   |

| 4-5  | Verification results for an influence-based cluster      | 89   |

| 4-6  | Influence-based clustering results for MIPS processor    | 90   |

| 4-7  | Verification results for an intersection-based cluster   | 91   |

| 4-8  | Intersection-based clustering results for MIPS processor | 91   |

| 4-9  | Property clustering and verification for MIPS processor  | 92   |

| 4-10 | Structure-based clustering results for OSES              | 93   |

| 4-11 | Textual clustering results for OSES                      | 93   |

| 4-12 | Influence-based clustering results for OSES              | 94   |

| 4-13 | Intersection-based clustering results for OSES           | 94   |

| 4-14 | Property clustering and verification for OSES            | 94   |

| 5-1  | Test generation results using intra learnings            | 113  |

| 5-2  | Test generation result for MIPS processor                | 117  |

| 5-3  | Test generation result for stock exchange system         | 118  |

| 6-1  | Test generation result for MIPS processor                | 136  |

| 6-2 | Test generation result for OSES                   | 138 |

|-----|---------------------------------------------------|-----|

| 7-1 | Assertion refinement for the router example       | 161 |

| 7-2 | RTL coverage for the router example               | 163 |

| 7-3 | Assertions refinement for the Alpha AXP processor | 164 |

| 7-4 | RTL coverage for the Alpha AXP processor          | 164 |

# LIST OF FIGURES

| Figu | ire                                                                            | page |

|------|--------------------------------------------------------------------------------|------|

| 1-1  | SoC design and validation flow                                                 | 15   |

| 1-2  | Comparison of functional validation between specification and implementation . | 18   |

| 1-3  | Top-down validation of SoC architectures                                       | 21   |

| 2-1  | Mapping from a SystemC structure to corresponding graph model                  | 26   |

| 2-2  | An example of data type transformation                                         | 28   |

| 2-3  | An example of SystemC TLM module                                               | 29   |

| 2-4  | An example of SMV module                                                       | 30   |

| 2-5  | An example of TLM process                                                      | 31   |

| 2-6  | An example of SMV process                                                      | 32   |

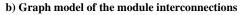

| 2-7  | UML activity nodes                                                             | 33   |

| 2-8  | The UML activity diagram of an ATM                                             | 35   |

| 2-9  | The generated skeleton after structure extraction                              | 42   |

| 2-10 | Translation rules for state and data transitions                               | 43   |

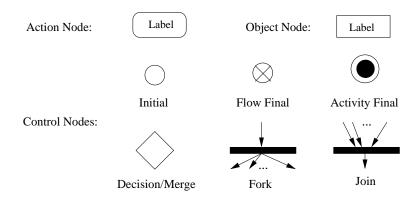

| 2-11 | The TLM structure of the router                                                | 45   |

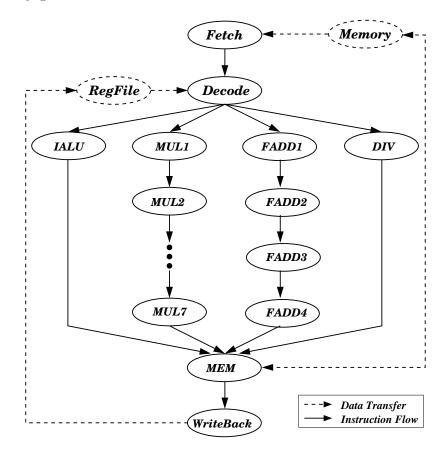

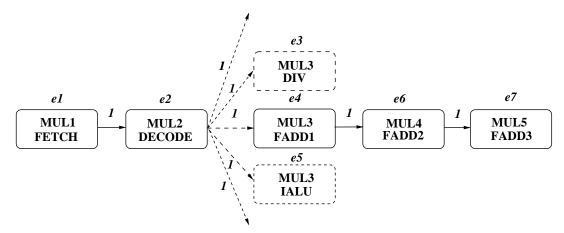

| 2-12 | Graph model of a VLIW MIPS processor                                           | 46   |

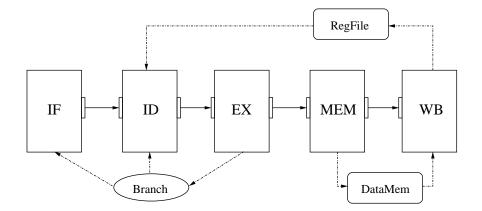

| 2-13 | TLM of the Alpha AXP processor                                                 | 47   |

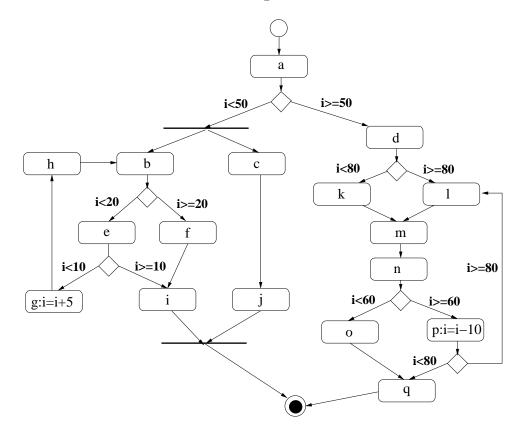

| 2-14 | The activity diagram for a control system                                      | 48   |

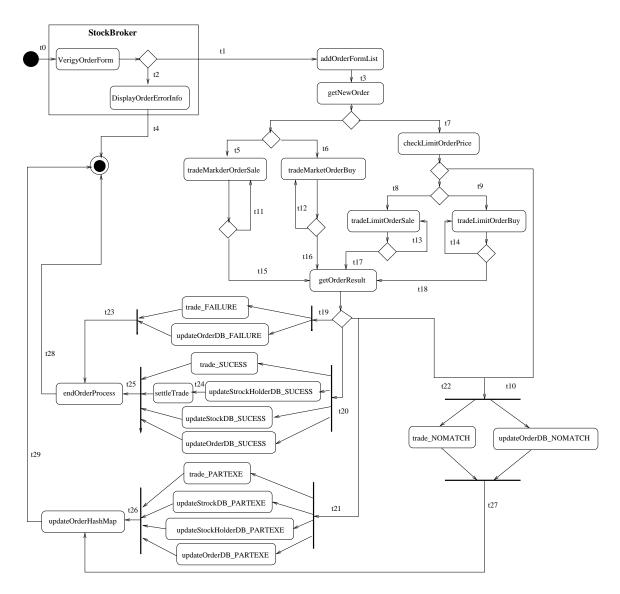

| 2-15 | The activity diagram for a stock exchange system                               | 49   |

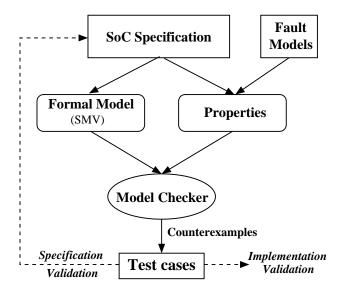

| 3-1  | Test generation using model checking                                           | 50   |

| 3-2  | Fault model examples                                                           | 55   |

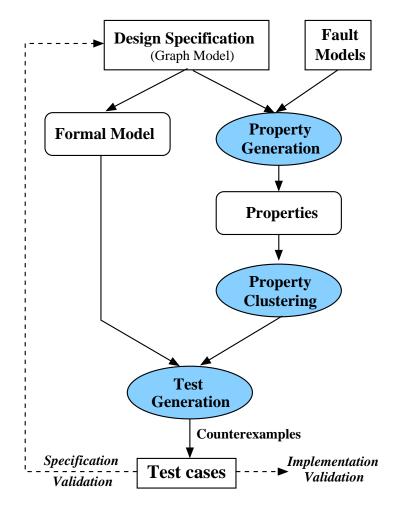

| 4-1  | Our test generation methodology                                                | 64   |

| 4-2  | Conflict analysis using an implication graph                                   | 68   |

| 4-3  | An example of name substitution                                                | 81   |

| 4-4  | An example of conflict clause reuse                                            | 84   |

| 5-1  | Two examples of SAT search                                                     | 99   |

| 5-2  | A scenario where bit-value ordering works                  | 100 |

|------|------------------------------------------------------------|-----|

| 5-3  | A scenario where bit value ordering fails                  | 101 |

| 5-4  | An example of bit-value and variable ordering              | 101 |

| 5-5  | An example of conflict clauses based variable ordering     | 102 |

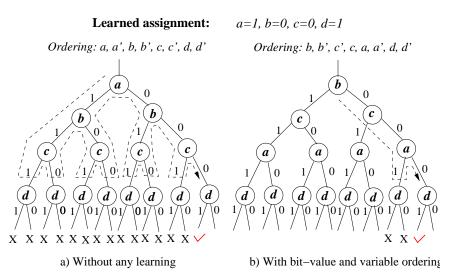

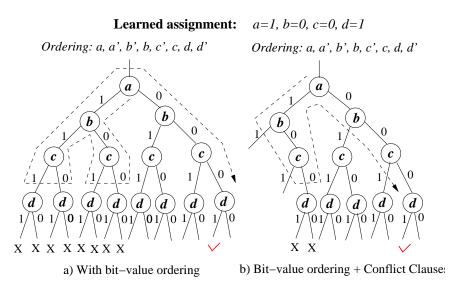

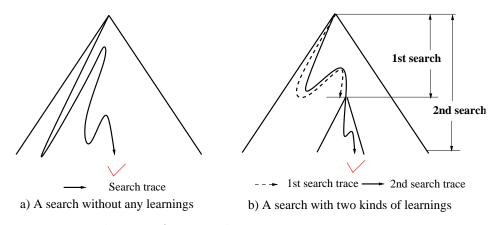

| 5-6  | Learning techniques for a single property                  | 106 |

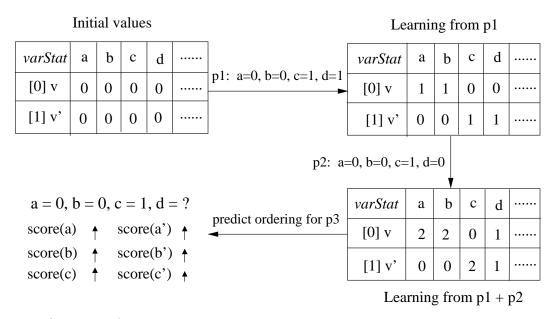

| 5-7  | Statistics for two properties                              | 108 |

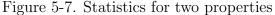

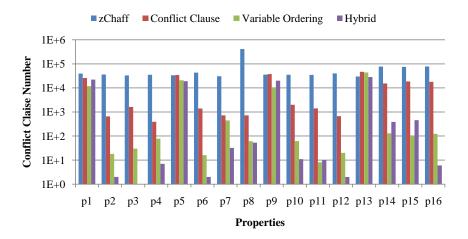

| 5-8  | Conflict statistics using various intra-property learnings | 114 |

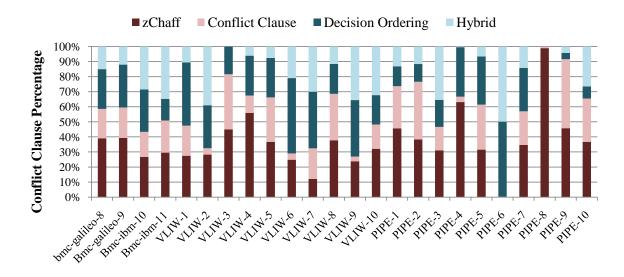

| 5-9  | Implication statistics using various intra-learnings       | 115 |

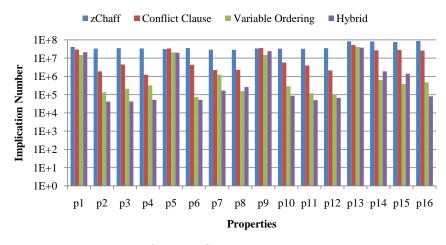

| 5-10 | Conflict statistics for MIPS processor                     | 116 |

| 5-11 | Implication statistics for MIPS processor                  | 118 |

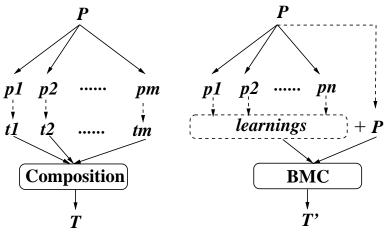

| 6-1  | Two property decomposition techniques                      | 120 |

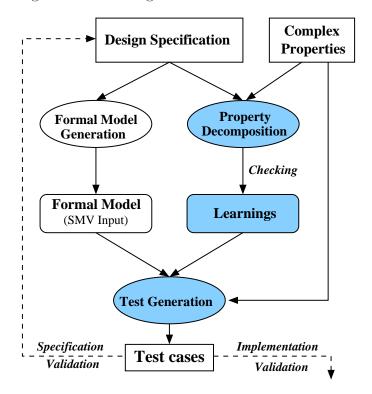

| 6-2  | Our test generation framework                              | 121 |

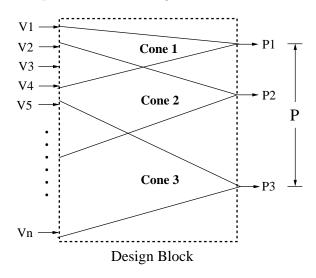

| 6-3  | The COI of a design block                                  | 123 |

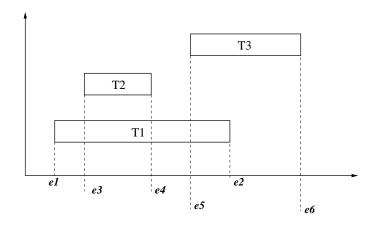

| 6-4  | A functional scenario with three transactions              | 124 |

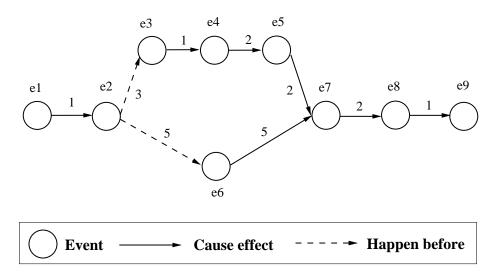

| 6-5  | A DAG of event relation                                    | 128 |

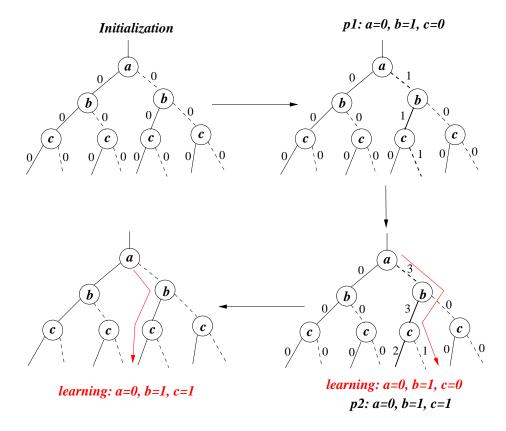

| 6-6  | Learning statistics applied on decision trees              | 131 |

| 6-7  | Event implication graph for property P                     | 135 |

| 6-8  | Property checking result for MIPS processor                | 137 |

| 7-1  | Our equivalence checking framework                         | 144 |

| 7-2  | The structure of our prototype tool                        | 152 |

| 7-3  | An example of assertion equivalence                        | 159 |

| 7-4  | The packet format of the router in TLM and RTL             | 160 |

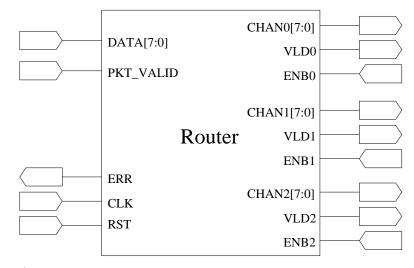

| 7-5  | The I/O interface of the router example                    | 161 |

| 7-6  | An example of TLM-to-RTL refinement                        | 162 |

## Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

# EFFICIENT APPROACHES FOR FUNCTIONAL VALIDATION OF SOC DESIGNS USING HIGH-LEVEL SPECIFICATIONS

By

Mingsong Chen

August 2010

## Chair: Prabhat Mishra Major: Computer Engineering

Increasing complexity coupled with time-to-market pressure create a critical need to raise the abstraction level for System-on-Chip (SoC) designs. Functional validation is widely acknowledged as a major bottleneck due to lack of automated techniques and limited reuse of validation efforts between abstraction levels. Simulation is the most widely used form of validation using random or constrained-random tests. Directed tests are very promising for simulation since only fewer directed tests are required compared to billions of random tests to achieve a coverage goal. Currently, directed test generation is performed manually which is time-consuming and error-prone. This dissertation presents a novel top-down methodology for automatically generating directed tests from high-level specifications and reuse them across different abstraction levels. The objective is to reduce the overall functional validation effort. My research has four major contributions: i) it proposes a method that can extract formal models from high-level SoC specifications; ii) it presents an approach that can automatically derive properties based on fault models; iii) it proposes efficient clustering, learning and decomposition techniques to reduce the directed test generation time; and iv) it provides validation refinement approaches to enable reuse of the system-level validation efforts for low-level implementation validation as well as to check the consistency between different abstraction layers. Our experimental results using both software and hardware benchmarks demonstrate that the proposed approaches can significantly reduce the overall validation effort.

### CHAPTER 1 INTRODUCTION

Functional validation <sup>1</sup> is widely acknowledged as a major bottleneck in System-on-Chip (SoC) design methodology – up to 70% of the overall design time and resources are spent on functional validation. In spite of such extensive efforts, majority of the SoC designs fail at the very first time (silicon failures) primarily due to functional errors [79]. The functional validation complexity is expected to increase further due to the combined effects of increasing design complexity and recent paradigm shift from single processor SoC designs to heterogeneous multiprocessor architectures [90].

Traditional SoC validation adopts a combination of simulation-based approaches and formal methods. Random testing is widely used for SoC simulation. In general, random tests can not guarantee the coverage and it may exercise the same functional scenario for several times because of randomness. Thus directed tests are a better alternative since only a small number of tests are required to achieve a functional coverage goal compared to random or constrained-random tests. However, due to lack of automated tools to generate directed tests, human intervention is necessary during the test generation. All these scenarios can lead to time-consuming and error-prone validation. My research targets to reduce the overall functional validation effort by automating various steps in the the validation flow as well as by developing efficient learning and reuse techniques.

The rest of the chapter is organized as follows. Section 1.1 presents the SoC design flow. Section 1.2 surveys the existing SoC functional validation methods. Finally, Section 1.3 presents the contributions of this dissertation.

<sup>&</sup>lt;sup>1</sup> The term "validation" generally refers to simulation-based approaches, while "verification" is used for both simulation-based and formal methods. This dissertation focuses on directed test generation for simulation, so it uses the term validation.

#### 1.1 SoC Design Flow

SoC integrates all components of a computer into a single integrated circuit (chip). It consists of both hardware (such as processor, memory and peripherals) and software (such as application programs). SoC may perform a variety of computations including digital, analog and mixed-signal functions. Thus it is widely used in the field of embedded and hybrid systems.

SoC is becoming increasingly complex since new applications require more features. As a result, extensive system-level simulations are required to make the right architectural trade-offs. To efficiently and quickly make the decision on these trade-offs, design architects increasingly leverage system-level specifications instead of implementations to perform such analysis.

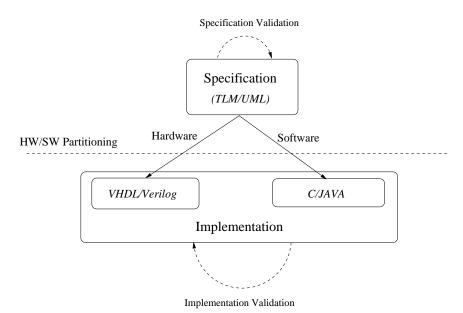

Figure 1-1. SoC design and validation flow

Figure 1-1 presents a SoC design and validation flow. Various hardware and software modeling paradigms are used for SoC specifications. Two of the most widely used specifications are Transaction Level Modeling (TLM) [16, 78] and Unified Modeling Language (UML) [69]. They establish a standard to enable fast simulation speed and easy model interoperability for hardware/software co-design. Generally, TLM is promising for

hardware modeling and UML focuses on software modeling. TLM mainly allows modeling of communication between different hardware components of a system and data processing in each component. UML can capture both structural and behavioral information of a software system. Validated specification can be used as a golden reference model for validation of software and hardware implementations. Although specifications can capture most important functional scenarios (system behaviors), some implementation details can be still missing. For example, TLM provides two kinds of modeling styles: loosely-timed models can be used to model the system behavior with less timing information and approximately-timed models can enable timing analysis of system behavior. Although TLM is promising for system-level modeling and simulation, it is still hard to accurately describe the hardware behavior because it lacks many detailed information such as timing details. So Register Transfer Level (RTL) is needed to model the implementation-level behavior after the system-level simulation. In Figure 1-1, the hardware part will be implemented using a RTL language such as VHDL or Verilog, and the software will be implemented using a programming language such as C or JAVA. Significant amount of validation work is needed to check the specified functional scenarios as well as to check the consistency between the specification and implementation.

#### **1.2** Functional Validation of SoC Designs

Specification validation is extremely important to ensure that the specified design is correct and can be used as a golden reference model for the implementation. According to [79], there are two key contributors to the SoC failures (silicon respin): specification errors and implementation errors. As expected, 82% of the designs with respins resulting from functional flaws had implementation errors. Interestingly, almost 47% of the designs with respins resulting from functional flaws had also incorrect or incomplete specifications [79]. Therefore, it is necessary to validate specifications before validating the implementation.

This section first surveys existing functional validation methods, and then describes several improvement opportunities to reduce the overall functional validation effort.

#### **1.2.1** Overview of Functional Validation Methods

Simulation is the most widely used SoC validation method. Compared to random testing methods which use billions of random and pseudo-random tests in the traditional design flow, directed tests are very promising in reducing the overall validation effort since a significantly smaller number of directed tests can achieve the same coverage goal [61]. However, a major problem in current directed test generation approach is that it is mostly performed by human intervention. Hand-written tests entail laborious and time consuming effort of verification engineers who have deep knowledge of the design under verification. Due to the manual development, it is infeasible to generate all directed tests to achieve a comprehensive coverage goal in a short time. Automatic directed test generation based on a comprehensive functional coverage metric is an alternative to address this problem.

Model checking [21] is one of the most widely used formal methods for automated test generation to validate software/hardware designs [5]. In the context of test generation, a design specification is described using a formal model. The required functional scenarios are described in the form of temporal logic formulas. When checking a false property using a model checker, one counterexample is reported to falsify the property. Because this counterexample is a sequence of variable assignments, it can be used as a directed test to validate the functional scenario of the specification. However, model checking based techniques do not scale well for large designs due to the "state space explosion"  $^2$ .

Simulation based methods are fast but cannot guarantee the convergence of functional coverage. Model checking based methods can automatically generate directed tests but cannot deal with large designs. Currently, most SoC validation approaches use a hybrid method which incorporates both techniques. The hybrid method first performs the

$<sup>^2</sup>$  The number of states generated for verifying a property is huge and can not be handled due to the memory capacity of computers.

random simulation to get as much functional coverage as possible. Then the uncovered functional scenarios and corner cases are activated using the directed tests.

#### **1.2.2** Potential Improvement Opportunities

Since system-level specification is treated as the golden reference model in the SoC design flow, a logic error in the system-level specification certainly will cause the malfunction in the implementation. Because implementations are more complex than system-level specifications, finding an error in implementations will be more time-consuming. So it is necessary to guarantee that system-level specification validation can cover as many functional scenarios as possible. In addition, the differences between specification and implementation limit the degree of validation reuse. In the absence of significant reuse of validation efforts between different abstraction levels, the overall functional validation effort will increase since designers have to verify the specification as well as its implementation.

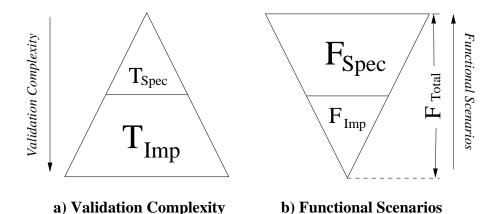

Figure 1-2. Comparison of functional validation between specification and implementation

Figure 1-2 compares specification and implementation levels. Assume that a

design D has a total F<sub>Total</sub> number of functional scenarios that need to be checked.

For specifications, there are F<sub>Spec</sub> number of functional scenarios that need to be checked,

and each specification level test generation need an average time of T<sub>Spec</sub>. In addition

to F<sub>Spec</sub> functional scenarios, there are F<sub>Imp</sub> functional scenarios need to be checked in

a) indicates that when checking a functional scenario, implementation validation is more difficult than specification validation. Figure 1-2 b)shows that specifications cover majority of the overall system functional scenarios (e.g., 70%), and implementations inherit all such scenarios with its own new additional functional scenarios (e.g., 30%) due to the introduction of implementation details. In this dissertation, the complexity of validating a functional scenario is equivalent to generating and applying a directed test. So test generation and corresponding simulation time is used to indicate the functional scenario validation effort.

In order to achieve a 100% functional coverage as well as to minimize the overall specification and implementation test generation time, it is necessary to find a method to optimize the Equation (1-1).

$$Minimize: F_{Spec} \times T_{Spec} + \{F_{Spec} + F_{Imp}\} \times T_{Imp}$$

$$Subject to: \begin{cases} F_{Spec} + F_{Imp} = F_{Total} \\ T_{Spec} < < T_{Imp} \\ F_{Spec} > F_{Imp} \end{cases}$$

$$(1-1)$$

For directed test generation, there are four feasible options. Table 1-1 compares these approaches.

- No optimization: Specification level test generation and implementation level test generation are independent, and in each level there are no optimizations.

- **Specification level optimization:** Specification level test generation and implementation level test generation are independent. The overall specification test generation time can be reduced by certain optimization methods.

- **Reuse between specification and implementation:** No optimization for specification and implementation level test generation, but the specification tests can be reused for implementation level validation.

- Specification level optimization + reuse between specification and implementation: Optimizations reduce the overall specification level test generation time, and the specification level tests can be reused for implementation level validation.

Assume that in system validation we can find a specification level test generation optimization that can produce  $\alpha$  times ( $\alpha > 1$ ) speedup, and we can obtain another  $\beta$ times ( $\beta > 1$ ) speedup due to validation reuse. According to the comparison shown in Table 1-1, the last option can achieve the best possible performance. The goal of this dissertation is to develop efficient techniques to reduce the overall validation effort using the fourth (last) option.

| Optimization                | Time                                                                                           |

|-----------------------------|------------------------------------------------------------------------------------------------|

| None                        | $F_{Spec} \times T_{Spec} + F_{Total} \times T_{Imp}$                                          |

| Specification level         | $F_{Spec} \times T_{Spec} / \alpha + F_{Total} \times T_{Imp}$                                 |

| Reuse                       | $F_{Spec} \times T_{Spec} + F_{Spec} \times T_{Imp}/\beta + F_{Imp} \times T_{Imp}$            |

| Specification level + Reuse | $F_{Spec} \times T_{Spec} / \alpha + F_{Spec} \times T_{Imp} / \beta + F_{Imp} \times T_{Imp}$ |

Table 1-1. A comparison for four optimizations

#### 1.2.3 Challenges

Each of the components (such as IP cores, processors and memories) in a SoC design can be verified using existing validation approaches. However, the validation of the overall system is extremely complex due to exponentially large number of possible interactions that are extremely hard to model, analyze and validate. Although the potential improvements proposed in the previous section seems promising, there are four fundamental problems in automated generation of directed tests for SoC architectures. The first challenge is to decide specification models for SoC architectures and how to verify the specification to ensure that it can be used as a golden reference model. The next challenge is to identify a comprehensive functional coverage metric to enable coverage-driven generation of properties and associated high-level tests. The third and most important challenge is how to significantly reduce the test generation complexity to avoid state space explosion problem. Finally, due to significant differences between specifications and implementations, a major challenge is how to efficiently reuse the specification-level properties and tests for validation of SoC implementations.

## **1.3** Dissertation Contributions

My research employs a top-down validation methodology using a combination of simulation based approaches and formal methods to address the four challenges mentioned in Section 1.2.3. The objective of my research is to develop tools, techniques and methodologies to enable automatic generation of directed functional tests to drastically reduce the overall verification effort as well as to improve the quality of SoC designs.

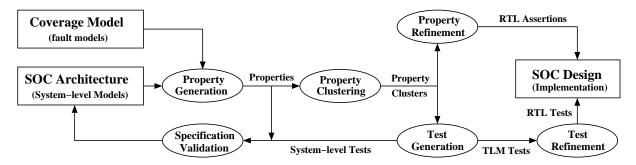

Figure 1-3. Top-down validation of SoC architectures

Figure 1-3 outlines the proposed validation methodology for SoC architectures using system-level specification. It consists of four major contributions as follows:

- Formal modeling of SoC designs: Since most existing SoC specifications are not formal enough to enable automated test generation, this dissertation proposes an approach for automatic specification analysis. It can extract formal models from semi-formal hardware and software specifications.

- **Coverage-driven property generation:** Functional coverage plays an important role to determine the adequacy of functional validation. This dissertation defines various fault models for SoC specifications. Based on these fault models, we can automatically derive properties to validate the specified functional scenarios.

- Efficient directed test generation: To reduce the overall test generation time for the same design with a large set of properties, this dissertation proposes various clustering methods which can cluster the similar properties together to share the learnings during test generation. The proposed framework investigates two kinds of learnings based on conflict clause forwarding as well as decision ordering. Such learnings can be used to avoid repeated validation efforts between similar properties. For complex properties without learning opportunity, this dissertation proposes two decomposition techniques that can actively achieve the learning to reduce its test generation time.

- Automated refinement of validation efforts: This dissertation develops a prototype tool which can automatically convert TLM level tests and properties into

RTL tests and assertions to enable implementation level validation. Based on this validation effort reuse, this dissertation proposes a methodology which can check the assertion-based functional equivalence between specifications and implementations.

The rest of this dissertation is organized as follows. Chapter 2 describes how to extract formal models from system level specifications of SoC designs. Chapter 3 describes how to generate properties based on our proposed fault models. Chapter 4 to 6 discuss how to efficiently generate tests to enable functional validation. Chapter 4 describes how to divide the properties into several groups such that each group contains similar properties that can benefit from each other during test generation. Chapter 5 presents the decision ordering based learning techniques which can drastically reduce the overall test generation time. Chapter 6 proposes various decomposition techniques to actively find the learnings for a complex property. Chapter 7 presents the methodology for automated property and test refinements. It also describes how to utilize the validation refinement for functional equivalence checking. Finally, Chapter 8 concludes the dissertation and outlines several future research directions.

## CHAPTER 2 FORMAL MODELING OF SOC SPECIFICATIONS

Modeling plays a central role in design automation of SoC architectures. It is necessary to develop a specification language that can model complex systems at a higher level of abstraction and also enable automatic analysis and generation of efficient reference models. The language should be powerful enough to capture high-level description of a wide variety of SoC architectures as well as should be simple enough to allow correlation of the information between the specification and the architecture/system manual.

As a system level specification, SystemC TLM [78] establishes a standard to enable fast simulation speed and easy model interoperability for hardware/software co-design. It mainly focuses on the communication between different functional components of a system and data processing in each component. Although UML is being used as a de facto software modeling tool, UML Profile for SoC [68] is proposed as an extension of UML 2.X to enable SoC hardware modeling. It can be used to capture the system behavior for both SoC software and hardware components [19, 65, 77]. However, both SystemC TLM and UML diagrams are not formal enough for automatic test generation using model checking techniques [5]. Consequently, the ambiguity, incompleteness, and contradiction in specifications can lead to different interpretations. Therefore it is necessary to formalize the semantics of SoC specifications.

This chapter introduces two widely used SoC specifications: SystemC TLMs for hardware modeling, and UML activity diagrams for software modeling. Next, it describes how to automatically extract the formal models from specifications to enable subsequent validation steps. The rest of the chapter is organized as follows. Section 2.1 introduces the formal modeling of SystemC TLMs. Section 2.2 proposes the formal modeling techniques of UML activity diagrams. Section 2.3 presents the case studies using both SystemC TLM designs and UML activity diagrams. Finally, Section 2.4 summarizes the chapter.

#### 2.1 Specification using SystemC TLMs

As a framework built on C++, SystemC [70] deliberately mimics the hardware description languages such as VHDL and Verilog. With an event-driven simulation kernel, SystemC can be used to simulate the behavior of concurrent processes which can communicate with each other using procedure calls or other mechanisms offered by the SystemC library. Generally, SystemC is often associated with Transaction-Level Modeling (TLM) [16, 78], because SystemC TLM provides a wrapper to facilitate the process of communication modeling. Since SystemC TLM provides a rapid prototyping platform for the architecture exploration and hardware/software integration [30], it is widely used to enable early exploration for both hardware and software designs. It can reduce the overall design and validation effort of complex SoC architectures.

To enable automated analysis, various researchers have tried to extract formal representations from SystemC TLM specifications. Abdi et al. [2] introduced *Model Algebra*, a formalism for representing SoC designs at system level. The work by Kroening et al. [48] formalized the semantics of SystemC by means of labeled Kripke structures. Moy et al. [64] provided a compiler front-end that can extract architecture and synchronization information from SystemC TLM designs using HPIOM. Karlsson et al. [41] translated SystemC models into a Petri-Net based representation PRES+. This model can be used for model checking of properties expressed in a timed temporal logic. Habibi et al. [34] proposed a method that adopts the formal model AsmL. A state machine generated from AsmL can be verified, and then can be translated to both SystemC code and properties for low level validation. All these modeling techniques focus on the formal modeling of SystemC specifications. However, none of them investigate the automated test generation for transaction validation. This section discusses how to extract the formal models from SystemC TLM specifications to enable automated test generation.

#### 2.1.1 Formal Modeling of SystemC TLMs

As a high level specification, SystemC TLM emphasizes the functionality of the data transfers instead of actual implementation. A SystemC TLM design interconnects a set of processes communicating with each other using transaction data token (i.e., C++ objects). The initial process starts a communication, and the target process passively responds to the communication. Similar to the producer/consumer models, each process does the following tasks: consuming data, processing data and producing data.

Since SystemC is based on C++, it supports various programming constructs (e.g., template, inheritance, etc.). Although the concept of some TLM components (signals, ports, etc.) is easy, their C++ implementation details are really complex. Therefore, directly translating their behaviors to enable automated validation is difficult. In our framework, we abstract such SystemC components and hide the implementation details using the pre-defined SMV constructs. Furthermore, the underlying complex SystemC scheduler aggravates the modeling complexity. For SystemC TLM, to mimic the parallel execution of processes, the SystemC scheduler activates the *ready-to-run* processes in a "non-deterministic" way. However, since SMV is parallel in essence, it is not necessary to model the SystemC scheduler explicitly.

For TLM, two most important factors are the transaction data token and the transaction flow. So the extracted formal model of TLM specifications should reflect both information. In our test generation framework, it is required that the extracted models can not only guide the generation of SMV specification, but also can be used to automatically derive the properties for TLM test generation. Definition 1 gives the formal model of SystemC TLM designs.

#### **Definition 1.** The formal model of a SystemC TLM design is an eight-tuple ( $\Sigma$ , P, T,

A, E, M, I, F) where  $\Sigma$  is a set of transaction data tokens.

•  $P = \{p_1, p_2, \dots, p_m\}$  is a set of places.

- $T = \{t_1, t_2, \dots, t_n\}$  is a set of transitions.

- $A \subseteq \{P \times T\} \cup \{T \times P\}$  is a set of arcs between places and transitions.

- $E = \{e_1, e_2, \dots, e_k\}$  is a set of arc expressions. The mapping  $Expression(a_i) = e_i$  $(a_i \in A, 1 \le i \le k)$  gives the enable condition  $e_i$  for  $a_i$ . A token can pass arc  $a_i$  only when  $e_i$  is true.

- $M: 2^{P \times \Sigma} \times T \to 2^{P \times \Sigma}$  is a function that describes the internal operations on input transaction data and output transaction data of a transition.

- $I \in 2^{P \times \Sigma}$  specifies the initial state.

- $F \subseteq 2^{P \times \Sigma}$  specifies the final states.

In our framework, we use the graph model as an immediate form to capture the execution as well as interconnection of processes.

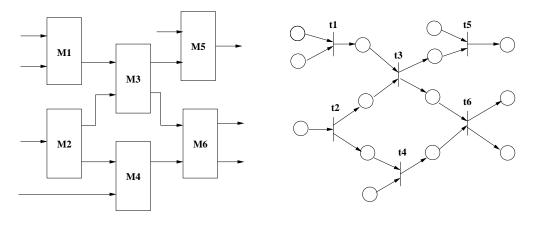

a) Interconnection of modules

Figure 2-1. Mapping from a SystemC structure to corresponding graph model

Figure 2-1a) shows an interconnection of six modules. Each arrow indicates a port binding between two modules. Figure 2-1b) shows the graph representation of its corresponding formal model. In the formal model, each circle is called a *place* that is used to indicate the input or output buffer of a module. It can temporarily hold the transaction data for later processing. The vertical bars are *transitions* which are used to indicate modules which contain processes to manipulate input and output transaction data tokens. The places without incoming arcs are *initial places* which start a transition. The places

without outgoing arcs are *target places*. A transaction data token flows from the initial places to the target places and token values may change in transitions when necessary. The internal logic of a transition determines the flow of the transaction.

#### 2.1.2 Transformation from SystemC TLM to SMV

Model checking techniques are very promising for directed test generation in hardware and software domains [5, 9, 71]. In our framework, we adopt SMV [56] as the formal specification to describe both the structure and behavior information of SystemC TLMs because of the following reasons. First, the underlying semantics of SMV is similar to the semantics of SystemC scheduler. So we can mimic most TLM's behaviors using SMV without modeling complex scheduler behavior. Second, SMV and TLM have the similar structure hierarchy. Each processing unit encapsulated by a TLM module corresponds to a SMV module. The interconnections (e.g. channels, ports and sockets) between TLM modules can be abstracted by using module parameters in SMV. Third, like SystemC, SMV provides a rich set of programming language constructs such as *if-then-else*, caseswitch and for loop statements. Fourth, SMV main module connects, similar to SystemC, each component of the system. Finally, SMV supports various kinds of data types and data operations. Especially users can define their own data type. All of these SMV features facilitate the translation from TLMs to SMV specification. It is important to note that, due to the expressiveness of the SMV language, currently our framework just supports loosely timed modeling. We are planning to use the timed automata checker (such as UPPAAL [8]) in our framework to enable the timing verification of transactions.

As an intermediate form for TLM to SMV translation, the graph model provides both structure and behavior information. Such information need to be collected for a translation to a SMV representation to enable automated directed test generation. The structure information includes the data type definition and connectivity between modules. It corresponds to the description of transaction data token as well as interconnection of transitions and places in the graph model. The behavior information contains token

27

processing and token routing. In the formal model, it represents the internal processing of a transition. This section discusses how to extract both structural and behavioral information and transform it to a SMV specification. We use the example shown in Section 2.3.1 to illustrate how to extract the formal model from a router example.

#### 2.1.2.1 Structure Extraction

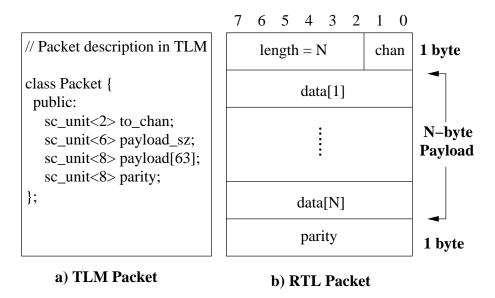

In TLM, the content of a transaction data token indicates the transaction flow and the output of each component. So it consists of the key part of TLM tests. Generally a transaction token consists of several attributes with different types. Because data type determines the size of the specified variable which in turn affects the model checking performance, it is necessary to figure out the data type of a token. Besides all native C++ types, SystemC defines a set of data type classes within the namespace  $sc_{-}dt$  to represent values with application-specific word lengths applicable to digital hardware. SMV also supports various data types such as array, Boolean, integer, struct and so on. Such data type definitions facilitate the mapping of data types between SystemC TLM and SMV specification. During the transformation, the word lengths of user-defined type need to be considered. Figure 2-2 gives an example of the router *packet* in the form of SystemC TLM and SMV respectively. For example,  $sc_uint < 2 > has 2$  bits and will be transformed to a range 0..3 in SMV.

| <pre>class packet{</pre>          | <pre>typedef packet struct{</pre>  |

|-----------------------------------|------------------------------------|

| public:                           |                                    |

| <pre>sc_uint&lt;2&gt; to_ch</pre> | an; to_chan : 03;                  |

| <pre>sc_uint&lt;6&gt; paylo</pre> | ad_sz; payload_sz : 063;           |

| <pre>sc_uint&lt;8&gt; paylo</pre> | ad[4]; payload : array 30 of 0255; |

| <pre>sc_uint&lt;8&gt; parit</pre> | y; parity : 0255;                  |

| };                                | }                                  |

| a)packet in Syste                 | mC TLM b) packet in SMV            |

Figure 2-2. An example of data type transformation

Derived from the base class *sc\_module*, TLM modules are the main processing units for the transaction data. Generally each *sc\_module* contains the definitions of processes whose types are *SC\_METHOD* or *SC\_THREAD*. Modules communicate with each other by sending and receiving transaction data tokens via output and input ports. SystemC provides a communication wrapper for the system components (modules). In SystemC, there exists various binding mechanism (e.g. port to export binding, export to export binding and port to channel binding) to establish interconnection between modules. Usually each binding corresponds to a channel such as a first-in-first-out (FIFO) channel to temporarily hold transaction tokens.

```

class router : public sc_module{

public:

sc_export<tlm_put_if<packet> > packet_in;

sc_export<tlm_fifo_get_if<packet> > packet_out0;

sc_export<tlm_fifo_get_if<packet> > packet_out1;

sc_export<tlm_fifo_get_if<packet> > packet_out2;

router(sc_module_name module_name);

void route();

private:

tlm_fifo<packet> chan0, chan1, chan2, input_;

packet tmp_packet;

};

```

Figure 2-3. An example of SystemC TLM module

Figure 2-3 shows the TLM module structure of a router. The class  $sc\_export$  can be used as a port to communicate with other modules. Because the interface type of port  $packet\_in$  is  $tlm\_put\_if < packet>$ , it is an input port. In contrast,  $packet\_outx$  (x=0,1,2) have the interface  $tlm\_fifo\_get\_if < packet>$ , so they are output ports. During the router communication, each connection between a port and an export uses a FIFO channel to temporarily hold a packet.

Structurally similar to SystemC TLMs, SMV specification is also modularized and hierarchically organized. So the extraction of structure information needs to map the TLM constructs into the right place of the SMV specification. Figure 2-4 shows the SMV module skeleton corresponding to example in Figure 2-3 after the structure extraction. In SMV, a module uses the parameters as the input and output ports to both communicate with other modules and configure the system status defined in the *main* module. In the example of Figure 2-4, the SMV module has one input port and three output ports. The type of the input and output ports is packet. All the declarations of member variables except for the FIFO channels are declared in the SMV specification. Because a FIFO channel together with its port pairs are abstracted as a SMV parameter, it is not necessary to create a variable in SMV explicitly. Based on context during the elaboration, some of the declared variables will be initialized. In SMV specification, each output ports and local variables need to be initialized. For example, *packet\_out0* is a parameter which refers to an output port, so it will be initialized with a value "0". In our framework, it is required that all such module connections should be defined in the module *sc\_top*.

```

module router(packet_in, packet_out0, packet_out1, packet_out2){

input packet_in : packet;

output packet_out0, packet_out1, packet_out2: packet;

tmp_packet : packet;

init(packet_out0):=0;

init(packet_out1):=0;

init(packet_out2):=0;

init(tmp_packet):=0;

......

}

```

Figure 2-4. An example of SMV module

#### 2.1.2.2 Behavior Extraction

TLM behavior describes the run-time information of TLM including transaction creation, transaction manipulation and module communication. Transaction creation initializes a transaction by creating a data token (i.e. a C++ object) with proper values. Transaction execution describes the transaction flow among the modules. A module is a container which has a cluster of relevant processes. Such processes will handle the incoming transaction tokens and decide where to send them according to the specified conditions. Thus different value of a token will lead to different transaction flows. In our current prototype release, there are two kind of process to another process, and 2) channel-based events triggered by the procedure call. For example, in the blocking mode, a process can fetch a transaction data token from the specified input port only when the corresponding channel is not empty. Otherwise, the operation "get" will be blocked until there is an event triggered by the "put" operation by other processes.

```

router::router( sc_module_name mname ): sc_module(mname){

packet_in(input_); packet_out0(chan0);

packet_out1(chan1); packet_out2(chan2);

SC_METHOD(route);

sensitive << input_.ok_to_get();

dont_initialize();

}

void router::route() {

input_.nb_get(tmp_packet);

if(tmp_packet.to_chan == (sc_uint<2>)0)

chan0.nb_put(tmp_packet);

else if(tmp_packet.to_chan == (sc_uint<2>)1)

chan1.nb_put(tmp_packet);

else chan2.nb_put(tmp_packet);

}

```

Figure 2-5. An example of TLM process

Figure 2-5 gives the module process *route* of the router example. The process receives a packet from the driver via channel *input\_*, and then it decides where to send data based on the packet header information *to\_chan*.

TLM modeling provides some synchronization mechanism for the communications between modules. As shown in Figure 2-5, the router can fetch the data from the FIFO queue  $input_{-}$  only when the driver put a package and the FIFO channel event  $ok_{-}to_{-}get$  is triggered. Thus the synchronization between two modules is implicitly achieved.

SMV supports many constructs similar to the common programming language such as *if-then-else*, *switch-case* and *for loop*. So these constructs facilitate the behavior modeling of processes from TLM to SMV specification. Figure 2-6 is the translated SMV specification of the TLM example presented in Figure 2-5. During the translation from TLM to SMV, we abstract a channel as an implicit buffer between two ports. So a SMV module will get the input data from its input ports. There is no mapping of the channel in transformed SMV specification. For example, the *tmp\_packet* is assigned the value of the *packet\_in* instead of the value of *input\_* shown in the TLM example in Figure 2-5.

```

module router(packet_in, packet_out0, packet_out1, packet_out2){

next(tmp_packet) := packet_in;

if(tmp_packet.to_chan = 0){

next(packet_out0) := tmp_packet;

next(packet_out1) := 0;

next(packet_out2) := 0;

}else if(tmp_packet.to_chan = 1){

next(packet_out0) := 0;

next(packet_out1) := tmp_packet;

next(packet_out2) := 0;

}else{

next(packet_out0) := 0;

next(packet_out1) := 0;

next(packet_out2) := tmp_packet;

}

}

```

Figure 2-6. An example of SMV process

### 2.1.3 A Prototype Tool For TLM to SMV Translation

We developed a prototype tool TLM2SMV which can transform SystemC TLM specifications to corresponding SMV models for automated directed test generation. The details of the implementation are described in Section 7.2.3.1.

#### 2.2 Specification using UML Activity Diagrams

Formal verification can be used to verify the correctness of specifications, so it can be used to guarantee the quality of UML models [84]. UML activity diagram adopts Petri-net semantics which is promising to describe the concurrent behavior [18, 51, 88]. There are several approaches that use model checking techniques to verify UML activity diagrams. Eshuis [75] presented a translation procedure from UML activity diagrams to the input language of NUSMV [20]. However, the translation is used to verify the consistency between UML activity diagrams and class diagrams. It focuses on checking the consistency between two different models. Guelfi and Mammar [31] provided a formal definition for timed activity diagrams. They outlined the translation from the semantic specifications into PROMELA - an input language of the SPIN model checker. Das et al. [22] proposed a method to deal with timing verification of UML activity diagrams. All these verification work primarily focus on checking the consistency or correctness of the model itself instead of generating directed test cases.

In this chapter, we adopt UML 2.1.2 [69] as our specification. To reduce the complexity of the testing work, we restrict our testing target and investigate a subset of activity diagrams. The subset mainly contains action nodes, control nodes, object nodes and control and data flow. Especially for the object node, we assume that it can hold at most one object at a time and it does not support *competition* and *data store*. This section first gives the notations used in UML activity diagrams. Then it presents the formal definitions of the UML activity diagrams. Finally, it describes the translation from UML activity diagrams to SMV formal models.

#### 2.2.1 Notations

UML activity diagram is used to coordinate the execution of actions. An action takes a set of inputs and converts them into corresponding outputs. An activity (behavior) consists of a set of actions and flow edges. The actions are connected by object flow edges to show how object tokens flow through and connected by control flow edges to indicate the execution order.

UML activity diagrams adopt the semantics like Petri-net [72]. It is a type of directed graphical representation. Tokens which indicate control or data values flow along the edges from the source node to the sink nodes driven by the actions and conditions. An activity

diagram has two kinds of modeling elements: activity nodes and activity edges. More specially, there are three kinds of nodes in activity diagrams:

- Action Node: Action nodes consume all input data/control tokens when they are ready, generate new tokens and send them to output activity edges.

- **Object Node**: Object nodes provide and accept data tokens, and may act as buffers, collecting data tokens as they wait to move downstream.

- **Control Node**: Control nodes route tokens through the graph. The control nodes include constructs to choose between alternative flows (decision / merge), to split or merge the flow for concurrent processing (fork / join).

Figure 2-7 shows the basic constructs of activity nodes. An action node is denoted by round cornered boxes. It represents an execution of operations on input tokens, and generated new tokens will be delivered to an outgoing edges. An object node denoted using rectangle boxes is used to temporarily hold the data tokens waiting to be processed or delivered. For simplicity, we assume that object nodes do not support *competition* and *data store* for test case generation. A flow in an activity starts from the initial node. When a token arrives at a flow final node, it will be destroyed. The flow final node has no outgoing edges, so there is no downstream effect. When no tokens exist in an activity diagram, the activity will be terminated. The activity final nodes are similar to flow final nodes, except that when a token reaches one activity final node, the entire flow will be terminated. Decision nodes and merge nodes use the same shape of diamond. Decision nodes choose one of the outgoing flows according to the value of Boolean expressions labeled on the outgoing edge. Merge nodes select only one of incoming flows to deliver to the next activity node. Forks or joins are shown by multiple arrows leaving or entering the synchronization bar, respectively, to describe the concurrent behavior of a system. When a token arrives at a fork node, it will be duplicated across the outgoing edges. Join nodes synchronize multiple flows. The tokens must be available on every incoming edge in order to be passed to outgoing edges.

Activity nodes are connected by activity edges along which tokens may flow under some condition. Activity edges include control and data flow edges as follows:

- Control Flow Edge: Control flow edges indicate the execution sequence of actions.

- **Object Flow Edge**: Object flow edges indicate the relation of data token transmissions. It provides the inputs to actions.

In our method, we simplify the syntax and semantics of UML activity diagrams. We combine the control and data token together as a new kind of token which contains both control and data information. Such token can flow through activity edges. In other words, we do not distinguish control flow edges and object flow edges in our framework.

Figure 2-8. The UML activity diagram of an ATM

Figure 2-8 shows an example which uses most of the elements shown in Figure 2-7. It describes the functionality of withdrawing money from an Automated Teller Machine (ATM) [26]. A user needs to enter the access code first. In case of failure, the user can input the access code again. The operation will abort if access code is wrong in both cases. If the input access code is right, the user can enter the amount of money he wants to withdraw. At the same time, the printer will be ready to print a receipt. Once the ATM decides whether there is enough money the user can withdraw, it provides the cash and generates the information for this transaction. Finally, the printer prints the receipt and the transaction is complete.

The token for this example contains the ATM transaction information such as the input access code and input cash amount, the context information such as the available cash amount and correct access code. In general, a token reflects all the data information required for this activity. Table 2-1 shows the composition of a token of the ATM activity diagram. It consists of 5 variables which will be used to make the decisions illustrated in Table 2-2.

Table 2-1. Break down of a token in Figure 2-8

| Variable                | Type    | Description                       |

|-------------------------|---------|-----------------------------------|

| access_code             | string  | user's access code                |

| $access\_code\_input$   | string  | user access code input            |

| $access\_code\_resolve$ | string  | user access code input correction |

| $amount\_input$         | integer | user cash amount input            |

| $amount\_available$     | integer | cash amount available             |

Table 2-2. Condition on the flow edges in Figure 2-8

| Activity Edge | Condition            | Description                             |

|---------------|----------------------|-----------------------------------------|

| t2            | incorrect            | $access\_code! = access\_code\_input$   |

| t3            | correct              | $access\_code = access\_code\_input$    |

| t4            | resolved             | $access\_code = access\_code\_resolve$  |

| t5            | not resolved         | $access\_code! = access\_code\_resolve$ |

| t7            | amount available     | $amount\_input <= amount\_available$    |

| t8            | amount not available | $amount\_input > amount\_available$     |

#### 2.2.2 Formal Modeling of UML Activity Diagrams

Without formalism, it is hard to describe and model the activity diagrams accurately. UML activity diagram itself is a semi-formal specification that cannot be directly mapped to a model checker input (e.g., SMV models). We use Petri-net as an intermediate formal model between activity diagrams and SMV model, because the Petri-net formalism can capture the major functional scenarios as well as guide the translation.

Definition 2 describes the relation between the activity nodes and flow edges with a Petri-net semantics. It does not model the full features of activity diagrams and formally depicts the static abstracted structure of activity diagrams which can be used to describe the scenarios that need to be tested.

**Definition 2.** An activity diagram is a directed graph described using eight-tuple (A, T, F, C, V, A,  $a_I$ ,  $a_F$ ) where

- $A = \{a_1, a_2, \dots, a_m\}$  is a set of action nodes.

- $T = \{t_1, t_2, \ldots, t_n\}$  is a set of completion transitions.

- F ⊆ {A × T} ∪ {T × A} is a set of flow edges between activity nodes and completion transitions.

- C = {c<sub>1</sub>, c<sub>2</sub>,..., c<sub>n</sub>} is a finite set of guard conditions. Here, c<sub>i</sub> (1 ≤ i ≤ n) is a predicate (expression) based on the input variables. There is a mapping from f<sub>i</sub> ∈ F to c<sub>i</sub>, referred as Cond(f<sub>i</sub>) = c<sub>i</sub>.

- Let V be the set of all possible assignments for input variables  $V_1, V_2, \ldots, V_k$  where k is a positive integer.

- M: A × V → V is a mapping that describes the value change of the input variables inside an activity node.

- a<sub>I</sub> ∈ A is the initial node, and a<sub>F</sub> ∈ A is the final node. There is only one completion transition t ∈ T and c ∈ C such that (a<sub>I</sub>, t) ∈ F, and for any t' ∈ T, (t', a<sub>I</sub>) ∉ F and (a<sub>F</sub>, t') ∉ F.

In our formalization, a node can be an action node, an initial node or a final node. We use the *completion transition* and *flow edge* to model the behavior of the control nodes. In the graph, the nodes are connected by flow edges associated with a completion transition. Because activity diagrams allow tokens to exist in the flows concurrently, the completion transition can be used to synchronize the token flows. If a completion transition has multiple incoming flow edges, it will do the join operation. If there are multiple outgoing flow edges, then it will do the fork operation. For each flow edge, there may be a condition which can guide the token traverse. The graph has one initial node that indicates the start of control and data flows. Activity diagrams have two kinds of final nodes: flow final nodes and activity final nodes. We combine them together and use a join operation to get a new activity final node. So in the definition there is only one final node.

When analyzing dynamic behaviors of an activity diagram, we need to use the states (a set of actions executing concurrently) to model the status of a system. Current state (denoted by CS) of an activity diagram indicates the actions which are being activated. **Definition 3.** Let D be an activity diagram. The current state CS of D is a subset of A.

For any transition  $t \in T$ ,

- •t denotes the preset of t, then •t = {  $a \mid (a,t) \in F$  }.

- $t^{\bullet}$  denotes the postset of t, then  $t^{\bullet} = \{a \mid (t, a) \in F\}.$

- enabled(CS) denotes the set of completion transitions that are associated with the outgoing flow edges of CS, then  $enabled(CS) = \{ t \mid \bullet t \subseteq CS \}$ .

- firable(CS) denotes the set of transitions that can be fired from CS, then firable(CS)={t | t ∈ enabled(CS) ∧ •t are all completed ∧ ∃ n ∈ A. Cond((t, n)) is satisfied ∧ (CS •t) ∩ t• = ∅}. After some t is fired, the new current state CS' = fire(CS, t) = (CS •t) ∪ t•.

The current state of an activity diagram indicates which activity nodes are holding the tokens. For example, when  $\{d, f\}$  is the current state of the activity diagram in Figure 2-8, two tokens are in the activity nodes d and f individually. At this time, only the transition associated with  $t_9$  is firable. If it is fired, then the next state is  $\{e, f\}$ .

Because of the inherent concurrency, several transitions can be fired at the same time. For an activity diagram, all the firable transitions in a state form a *concurrent transition*. **Definition 4.** Let D be an activity diagram. For a state CS of D, a concurrent transition  $\tau$  is a set of completion transitions  $t_1, t_2, ..., t_n \in firable(CS)$  where

1.  $\forall i, j (1 \leq i < j \leq n), \bullet t_i \cap \bullet t_j = \emptyset;$

2.  $\forall t \in (enabled(CS) - \{t_1, t_2, ..., t_n\}), \text{ there exists } i \ (1 \leq i \leq n) \text{ such that } \bullet t \cap \bullet t_i \neq \emptyset.$ After firing  $\tau$  from state CS, the current state  $CS' = fire(CS, \tau) = \bigcup_{i=1}^{n} (fire(CS, t_i)) = \bigcup_{i=1}^{n} (fire(CS, t_i)) \cup t_i^{\bullet}).$

An instance of dynamic behavior of an activity diagram can be represented by a sequence of states and concurrent transitions. We call it a **path** of the activity diagram. Because a path may have cycles, during the model checking, it is hard to determine the cycle numbers, so we neglect the cycles on a path. We call such a path as **key path**.

**Definition 5.** A path  $\rho$  of the activity diagram D is a sequence of states and concurrent transitions, let

$$\rho = s_0 \xrightarrow{\tau_0} s_1 \xrightarrow{\tau_1} \dots \xrightarrow{\tau_{n-1}} s_n$$

where  $s_0 = \{a_I\}$ ,  $s_n = \{a_F\}$ , and  $s_{i+1} = fire(s_i, \tau_i)$  for any  $i \ (0 \le i < n)$ .  $\rho$  is a key path if there is no state repetition in  $\rho$ , i.e.  $\forall i, j \ (0 < i < j \le n), s_i \ \bigcap \ s_j = \emptyset$ .

There are five key paths in Figure 2-8:

•

$$\rho_1 = \{start\} \xrightarrow{\{t1\}} \{a\} \xrightarrow{\{t2\}} \{b\} \xrightarrow{\{t5\}} \{end\}$$

- $\rho_2 = \{start\} \xrightarrow{\{t1\}} \{a\} \xrightarrow{\{t3\}} \{c\} \xrightarrow{\{t6\}} \{dummy, f\} \xrightarrow{\{t7\}} \{d, f\} \xrightarrow{\{t9\}} \{e, f\} \xrightarrow{\{t10\}} \{g\} \xrightarrow{\{t11\}} \{end\},$

- $\rho_3 = \{start\} \xrightarrow{\{t1\}} \{a\} \xrightarrow{\{t3\}} \{c\} \xrightarrow{\{t6\}} \{dummy, f\} \xrightarrow{\{t8\}} \{e, f\} \xrightarrow{\{t10\}} \{g\} \xrightarrow{\{t11\}} \{end\},$

- $\rho_4 = \{start\} \xrightarrow{\{t1\}} \{a\} \xrightarrow{\{t2\}} \{b\} \xrightarrow{\{t4\}} \{c\} \xrightarrow{\{t6\}} \{dummy, f\} \xrightarrow{\{t7\}} \{d, f\} \xrightarrow{\{t9\}} \{e, f\} \xrightarrow{\{t10\}} \{g\} \xrightarrow{\{t11\}} \{end\},$

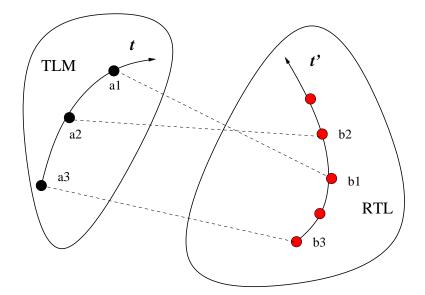

- $\rho_5 = \{start\} \xrightarrow{\{t1\}} \{a\} \xrightarrow{\{t2\}} \{b\} \xrightarrow{\{t4\}} \{c\} \xrightarrow{\{t6\}} \{dummy, f\} \xrightarrow{\{t8\}} \{e, f\} \xrightarrow{\{t10\}} \{g\} \xrightarrow{\{t11\}} \{end\}.$